- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello everyone,

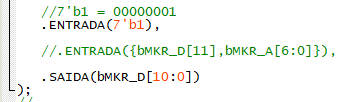

I'm trying to connect these pins I have inside a schematic ( images "input" and "ouput" ) to corresponding pins in my board, as shown in the "code verilog" image. The names "bMKR_A" and "bMKR_D" are the board's pins and they're already declared, the board is Arduino MKR Vidor 4000.

Problems is I can't seem to access the bits or parts of the vector inside of each bus to the corresponding pin. My only issue here is the ".ENTRADA[0]" part of the ".ENTRADA[0] (bMKR_A [0])," like lines, I know the rest is correct due to trial and error, but I don't know how to assign each individual bus.

What am I missing? Do I need to declare ENTRADA and SAIDA like

wire [7:0] ENTRADA;

wire [11:0] SAIDA;

before I access them? Because I did that and I still get the same error in line 173.

Thanks in advance for anyone taking the time to read this,

Ricardo Neto

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm not sure why you're using both a schematic and HDL code. From the code images, the ENTRADA and SAIDA signals are the I/O of an instantiated block. Is the code you are showing your top-level design and you've instantiated the schematic design in it? If so, yes, you would need to define ENTRADA and SAIDA with wire data types. Can you post more code, like the top-level design?

In any event, use the Pin Planner from the Assignments menu to make pin assignments.

And you mention an error but you don't mention what the error is. I think a little more detail is required here.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@RNeto2 , unless I'm completely misunderstanding you, it sounds like you are trying to access the FPGA IO pins via a Verilog program. But nothing you've provided allows you to do that. The top level HDL program will not have a port map as in the code you've provided. Instead, you tell it the pins in a constraint file (or via pin planner as @sstrell ). But your "schematic" does not list the FPGA pins. You need to trace it back to where it connects to the FPGA.

I'm assuming you are new to FPGA's ? It's too much to explain in a forum post. Altera has some outstanding free training found here:

https://www.intel.com/content/www/us/en/programmable/support/training/catalog.html

The "Become an FPGA Designer in 4 hours" is great as are most of the others.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As per my understanding you are facing issue while instantiating the Ord5_FIR_direct module & that too during compilation itself.

what errors you are getting while compilation? if possible share here HDL file in code snippet

you can try like below temporary wires duing instantiation at place of bMKR_A & bMKR_D & assign these wires to ports pin ENTRADA & SAIDA respectively in your top module & this is my guess since we don`t have clear picture of top module.

wire [7:0] temp_A;

wire [11:0] temp_D;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Have you resolved the issue or do you need support?

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you all for the replies, I am indeed a beginner in FPGAs and Verilog, so I appreciated all the input and the opportunity to read up more on the subject. A bit more reading drove me straight to the solution and I ended up fixing it as such:

A simple syntax issue, now the buses from my schematic fully align with my pins and I ran the code successfully. I will probably end up taking the free training courses to avoid more simple issues like this.

Also, I am using both schematic and HDL solely due to the visual aspect and the low complexity of the project ( it's just a low pass filter ).

Ricardo

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page