- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

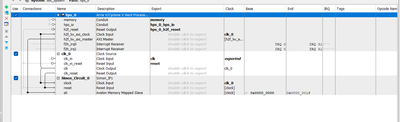

I am using the DE1-SoC board and trying to add a custom component in the platform designer. I used the GHRD that came with the board. I added a screenshot for this.

However, what I am supposed to do after when I "generate HDL", as in what changes do I need to make to the verilog file(if any) that comes in the GHRD. If I were to compile the project as is, I get errors about pin assignments and "design to large to fit in device".

How to fix this?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So you created your custom component and used the Component Editor to bring it into PD. Does your custom component require I/O pins? If so, you would need to export those signals from the component, usually by setting those signals as part of a conduit interface and then exporting from PD.

Did you make adjustments to the HPS I/O pin usage in the HPS parameters?

Also, did you intend to connect your custom component to the lightweight bridge of the processor (usually used just for CSR access of a component) or should you be enabling the regular h2f bridge for high-speed data transfer?

Maybe more detail of what your design goal here is would be helpful. Also, exact error messages from the tool would help as well.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi I get error messages about "design too large to fit in device". How can I modify my VHDL circuit to fit inside the FPGA, for example do I need to work on reducing variables, signals or process blocks etc?

My VHDL circuit has been tested many times with testbench in Questasim and works as expected but cannot seem to synthesized.

Please reply I am waiting.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Again, more info needed, maybe some code snippets or screenshots of all the error and warning messages you are getting. Just saying "design too large to fit in device" without any context of other messages, compilation report details, or code makes it very difficult to figure out what's going on. You also mentioned you get errors about pin assignments. What are those errors?

You could also try synthesizing the code outside of the Component Editor directly in Quartus. Create a dummy project and set your custom design as top-level. See if you get more detailed info about any issues with your design when you do that.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

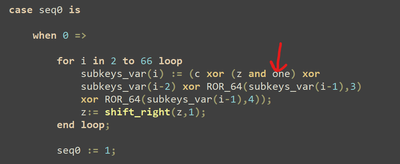

Ok I will try the dummy project approach, meanwhile I attached my entire error log and VHDL code. Have a look.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

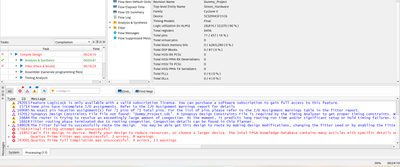

Ok this is the result of compiling the dummy project in Quartus. The VHDL circuit DOES NOT synthesize.

Can you tell me more about "LABS" and how I can reduce it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

LABs are logic array blocks. And yeah, your design is simply too big for the device you're targeting. It really was that simple! This design along with the Platform Designer interconnect needed to support it and connect to the HPS is too much for this device.

Your code looks pretty good. I don't see a lot of deep embedded if statements other than for your control signals, which is good.

But you do have large 64 bit functions and large loop iteration counts.

And why do you need 64 bits to represent "one"?

Try enabling Aggressive Area optimization in the Compiler Settings (that may be in Pro since that's what I normally use, but there should be a similar setting in Standard).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

"And why do you need 64 bits to represent "one"? "

This is because I can't figure out a way to perform computations using 64-bit values with the number 1 as B"01", if I try that then I see a "X" symbol in Questasim. If you have a better idea then let me know, that could be the difference lol.

I tried the aggressive area setting and after 20 minutes of misery it yielded no results. What is your advice for modifying my code so it can fit?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm not support. I'm a guy on the internet.

Your design files for simulation and synthesis don't have to be exactly the same. Just use a single bit for 1 for synthesis. You'll get warnings in Quartus about mismatched bit widths, but you can ignore that.

If area optimization didn't work, I'm not sure what else to tell you. Your design is just too big for this device.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Its okay now the problem is fixed. I simply replaced some of the large variables with signals and now the design fits. Can you tell me about block RAM and what name I need to use so the synthesizer can identify it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks sstrell for the support in the community.

areebTAG, do you still need help for this issue. I will close this thread if no further question.

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page