- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

1) Background: From the design assistant report there are a couple of signals listed where I really think signal skew needs to be reduced as much as possible but most of them would not profit.

2) Searching high and low, I cannot find any hint on how to promote a signal to use global clock resources or for that matter to demote signals to NOT use global clock resources.

3) I assume that in fact global clock resources are used automatically as much as possible. I say that, because most of the reported signals are actually contained in multiple instances of the same Verilog module. But only half of the instances I am actually using show up in the list. That tells me the other half was satisfactorily routed and the fitter simply ran out of resources on the chip.

4) assuming I am correct with #3, then the problem is not really promoting signals to use global clock lines, but in the contrary to demote signals. This is necessary, since these signals will not benefit from low skew, while signals that need it do not get the benefit.

Lien copié

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi,

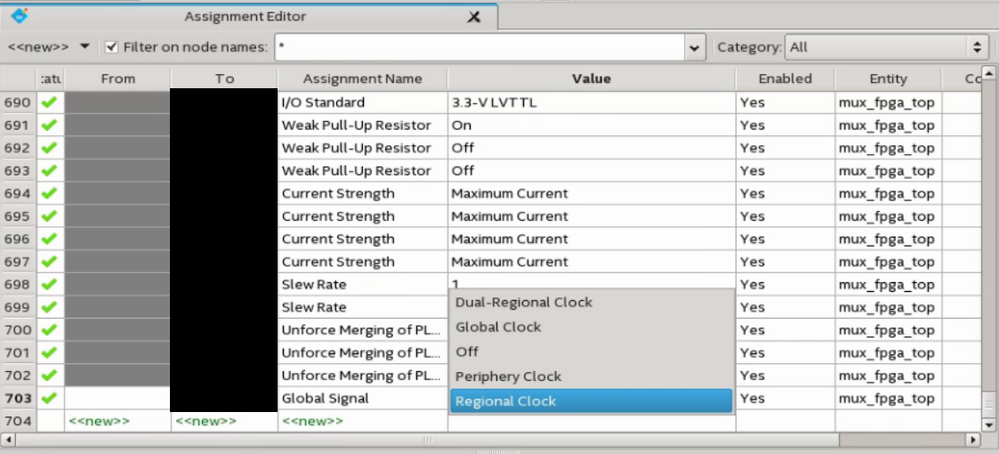

You may set the signal to use Global signal in Assignment Editor. To open Assignment Editor, click on Assignment > Assignment Editor

Setting the value to Off will prevent the Auto Global options from using the signal as automatic global signal.

Thanks.

Best regards,

KhaiY

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Thank you KhaiY, that helped. Sometimes Quartus is a bit of a maze ~:o)

Followup question: is it possible to do this in Verilog source code, similar to setting I/O pin logic levels and pin assignments?

Elmar

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

OK, I found out on my own.

- you cannot turn this off for individual signals in the source code

- turn off automatic global assignment on the project level (in the .qsf file or in the assignment editor). -> set_instance_assignment -name AUTO_GLOBAL_CLOCK OFF -to *

- now no signal is automatically promoted and you can set specific signals to use global routing resources. This can be done in the assignment editor as described above or with attributes in the source code -> (* altera_attribute = "-name GLOBAL_SIGNAL GLOBAL_CLOCK" *)

More details about Verilog HDL attributes can be found here: https://www.intel.com/content/www/us/en/programmable/quartushelp/17.0/hdl/vlog/vlog_file_dir_attribute.htm

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi,

Yes. It is glad that you found the answer for the new questions. Thanks for sharing this out with the link . This is beneficial to other users.

Thanks.

Best regards,

KhaiY

- S'abonner au fil RSS

- Marquer le sujet comme nouveau

- Marquer le sujet comme lu

- Placer ce Sujet en tête de liste pour l'utilisateur actuel

- Marquer

- S'abonner

- Page imprimable