- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm running Quartus 18.1 Std and the project is targeted to MAX10 device. I need to use ALTPLL from the standard IP Catalog. On the previous Quartus versions I used Megawizard to configure/instantiate the IP, now Quartus is doing the same from the IP Catalog itself and starts Megawizard in the background. It's fine.

It generates *.cmp, *. ppf, *.qip and *.vhd as expected. My problem is the absence of a simulation model for Modelsim. I don't see any options to tell the "Megawizard" to do it.

Please assist.

- Tags:

- ip

- megawizard

- quartus

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Message was deleted

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Since you are using Quartus standard, try to use the Nativelink simulation flow.

The NativeLink feature automatically compile your design, Altera IP, simulation model libraries, and testbench.

Questa Intel FPGA Edition Simulation Flow

Lite/Standard Edition:

https://www.intel.com/content/www/us/en/docs/programmable/703090/21-1/simulation-quick-start.html

https://www.youtube.com/watch?v=PmVVXQchv2c&t=39s

Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Richard,

I am not using Quartus in simulation flow - my main front-end design tool is HDL Designer. I found integration with Modelsim/Questa in this case much better and the flow and tools mainly are staying the same for different manufacturers. It can be a subjective opinion.

I'd like to get an answer on a much more isolated issue - why the "Megawizard" doesn't generate a simulation model? How to fix the problem without changing the design flow?

The problem described above is not related to ALTPLL only, the same behaviour was detected for FIFO and a few other IPs.

Kind Regards,

Leon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

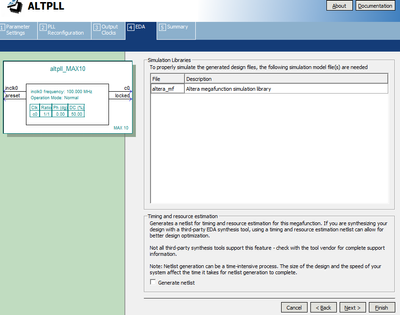

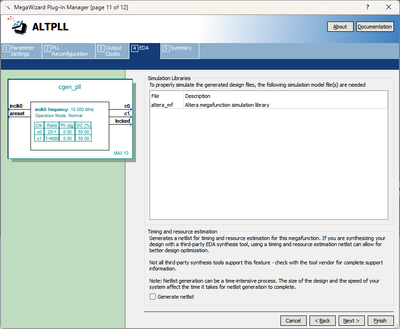

Which Quartus version are you using when the simulation files is generated ? How does it look like ?

I open in Quartus 21.std and it mentioned that altera_mf is needed. And this libraries is pre-compiled in the Questa Intel FPGA Edition.

Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It looks exactly the same as your screenshot (below is my screenshot):

Must the altera_mf be pre-compiled (before creating the custom IP)?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Must the altera_mf be pre-compiled (before creating the custom IP)?

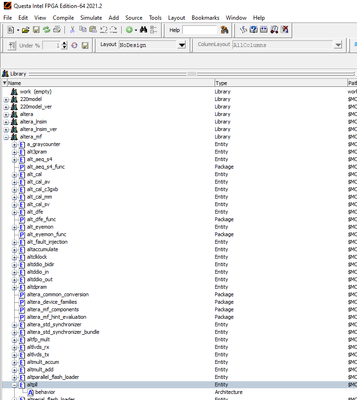

> It only pre-compiled in the Questa Intel FPGA edition (including Modelsim Intel FPGA edition). Other third party simulator tool will need to compile the libraries. The simulation libraries can be found at the quartus installation directory .../quartus/eda/sim_lib

Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Richard,

I'm not simulating anything yet - the project is in a very early stage, and practically the project doesn't exist yet. It is obvious, that I'll need to have compiled altera_mf to run a simulation, but I don't understand how the presence or absence of this compiled library can affect the "Megawizard" behaviour.

I will repeat myself and describe my question more generically: why does the "Megawizard" not generate the simulation (behaviour) model and how to fix it?

In the project, I'll need a few more IPs from IP Catalog (FIFO, LPM_SHIFTREG etc.) and I'd like to resolve the problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The Megawizard does not generate simulation model unfortunately.

Newer device like Arria 10 with the IP Parameter Editor has the option to do that but some older/legacy devices that use megawizard does not have the flexibility to do so.

I don't quite understand your intention when you said you are not simulating anything. What would you like to achieve by generating the simulation model for IP?

Most people generate the simulation model to simulate the IP and test the IP functionality.

Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My intention is exactly as you described: "to simulate the IP and test the IP functionality". It's the 1st task. The 2nd one is a simulation of higher-level subdesigns and, finally, a complete project. I'm not simulating anything at the moment.

About your info "older/legacy devices that use megawizard does not have the flexibility to do so". Isn't it contradicting with info provided on the web page https://www.intel.com/content/www/us/en/docs/programmable/683463/23-4/generating-ip-simulation-files.html and some others (for example ug_intro_to_megafunctions-683102-773176.pdf chapters 1.4 & 1.5)?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My statement "Newer device like Arria 10 with the IP Parameter Editor has the option to do that" is referring to the link that you provided. The first document link provided is based on Quartus Pro and there is no megawizard exist anymore with Pro. Also, you can see the figure.9 under section 1.5 in the ug_intro_to_megafunctions-683102-773176.pdf is the so called IP Parameter Editor, again not megawizard. You will notice that those "IP Parameter Editor" GUI comes with the "Generate HDL" button, which has the capability to generate the simulation model.

Try to compare the difference in the IP Parameter Editor vs Megawizard GUI (new vs old). Hope that clarify.

If you want to simulate and test the IP functionality, just use the Nativelink simulation flow that I mentioned previously, with the standalone IP in the project. (Nativelink only work in Standard)

It will work like a charm.

Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dropping a note to ask if my last reply was helpful to you?

Do you need any further assistance from my side?

Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I believe your inquiry has been answered. Now, I will transition this thread to community support. If you have any further questions or concerns, please don't hesitate to reach out.

Thank you and have a great day!

Best Regards,

Richard Tan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page