- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After creating the list of modifications in the ECO file using Change Manager in Chip Planner, I exported the modifications as a tcl file.

But I can’t import this file into the project. After starting it through the TCL sripts built-in utility, an error appears on the command line:

<Error: ERROR: Unable to find Chip Planner netlist. Read the netlist by using the "read_netlist" command.>

Inside the tcl file, the read_netlist command is executed. And of course I am doing a full compilation of the project before this

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know which edition and version of the software you are using? Could you provide a sample test case and steps to reproduce the error?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the answer. The problem was in environment variables for Windows. It was necessary to indicate the path for Quartus.

But now i have another problem. After applying ECO modifications the refitting of the project is carried out.

As a result, my LogicLock areas are ignored.

Is there any way to keep them in this situation?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I created a test case using the Pro Edition v19.3 and made the ECO changes using .tcl. The logic lock remains after applying the ECO. May I know which edition and version of the software you are using? Can you share the teat case you are using and the steps to reproduce the error?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

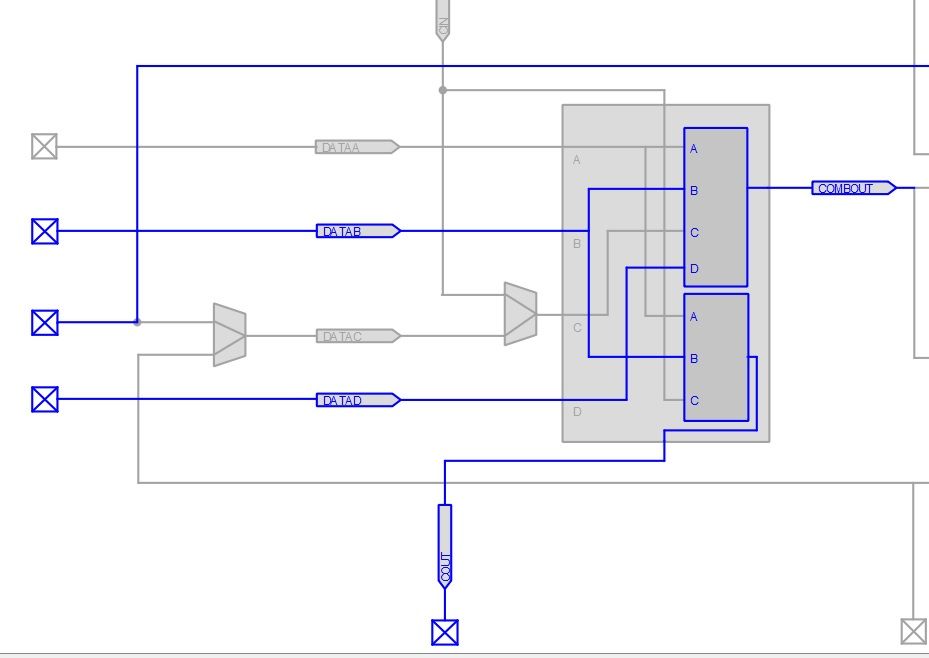

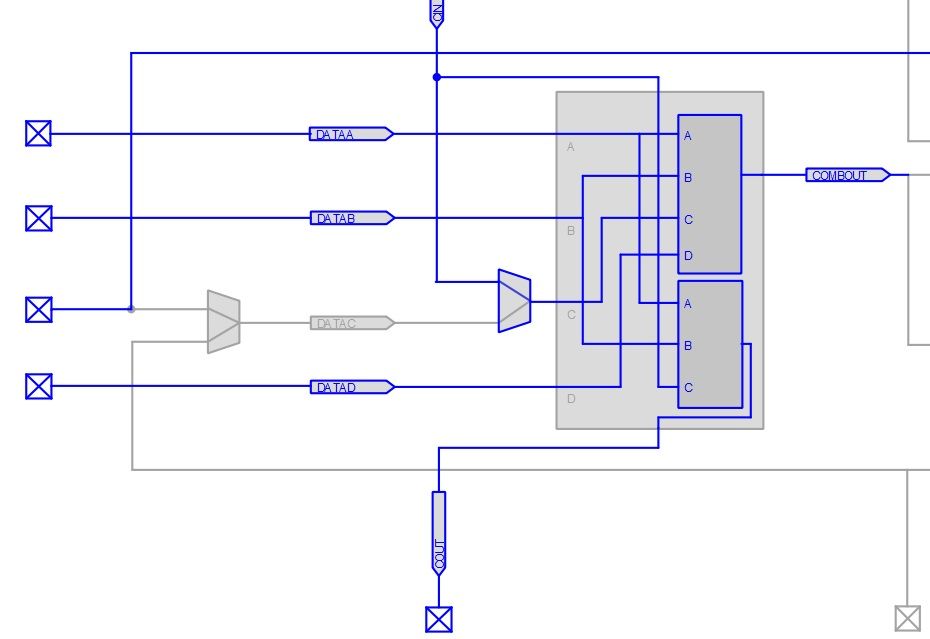

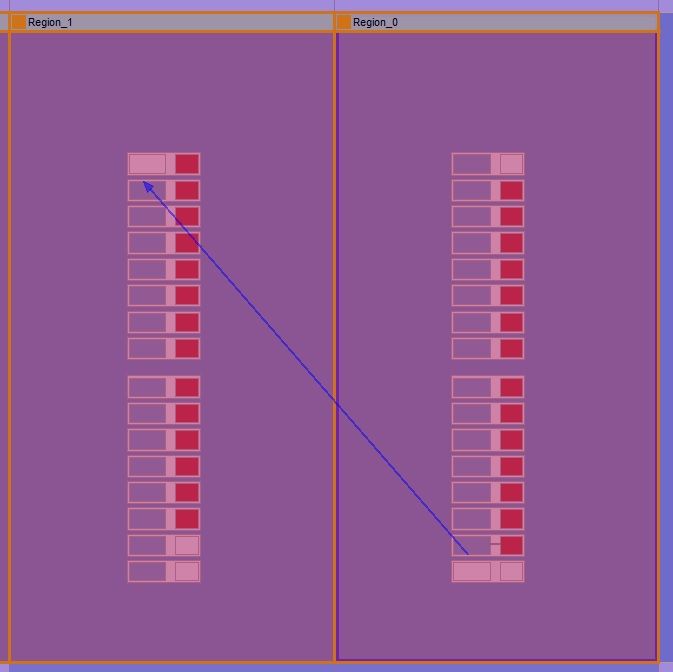

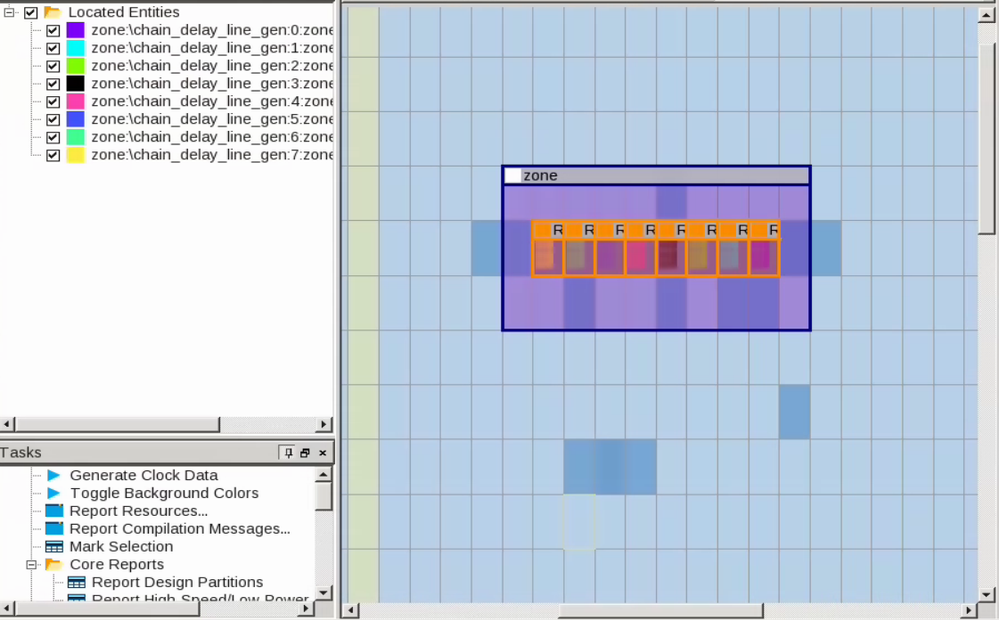

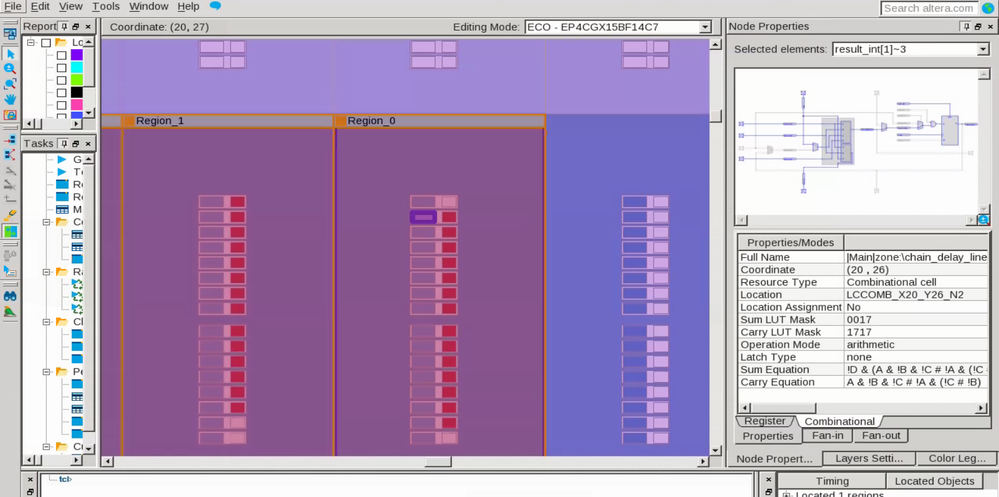

the problem appears in case of a change in the structure of the adder. Each adder is placed in a specific LAB using LogicLock.

The first cell of each adder always has Operation Mode: Normal.

Subsequent cells have Operation Mode: Arithmetic.

The last cell in LAB again has Operation mode: Normal.

I need each adder to be connected via Cin / Cout carry chains and not through Combout / DataABCD.

As a result of the corrections in the Resource Property Editor, I delete the LEs that work in normal mode and connect each LAB through the carry chains.

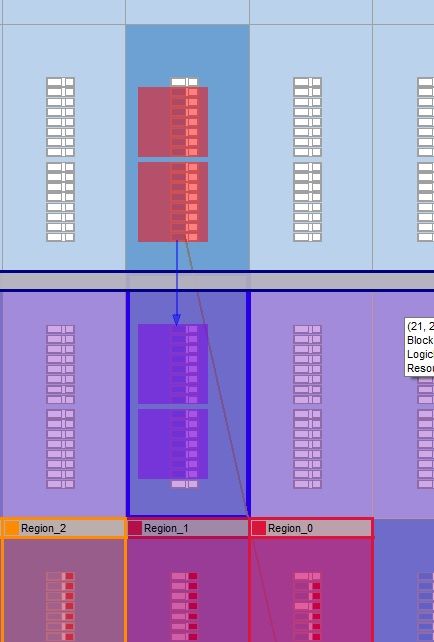

But after executing "Check And Save netlist", fitter cannot route every adder in the specified LAB, but route them outside of LogicLock. In this case, the adders are routed vertically, not horizontally.

I guess the problem is not with LogicLock itself, but with the principles of the LE structure.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may share the test case, steps and software version/edition, I can help to replicate here.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the attachment. Could you share the steps to reproduce the error? I tried to run the .tcl file but internal error occurred.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

first I do a full compilation of the project in Quartus. Then close the quartus, execute the move_mod.tcl script using cmd.exe.

For this, I execute only one command "quartus_cdb -t move_mod.tcl".

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I did the steps below:

- Compile the design in the Intel Quartus Prime software

- Close the software

- Execute the command: quartus_cdb -t move_mod.tcl

- Open the modules that are Logic Lock in Chip Planner

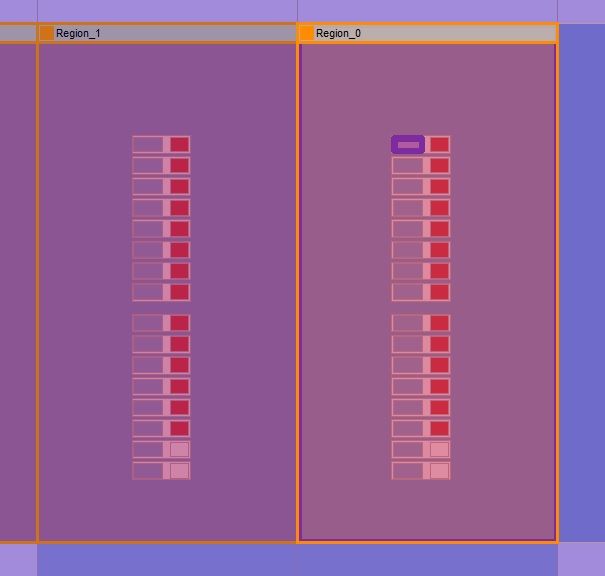

The modules are located within the logic lock area. See screenshot below.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Then you need to do a series of actions, which I described in my message with screenshot. When changing the structure of one of the area, you will get a fitter error

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I checked the cells in Region_0 and Region_1; all of them are in Arithmetic operation mode. May I know in which module you modify the cell?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

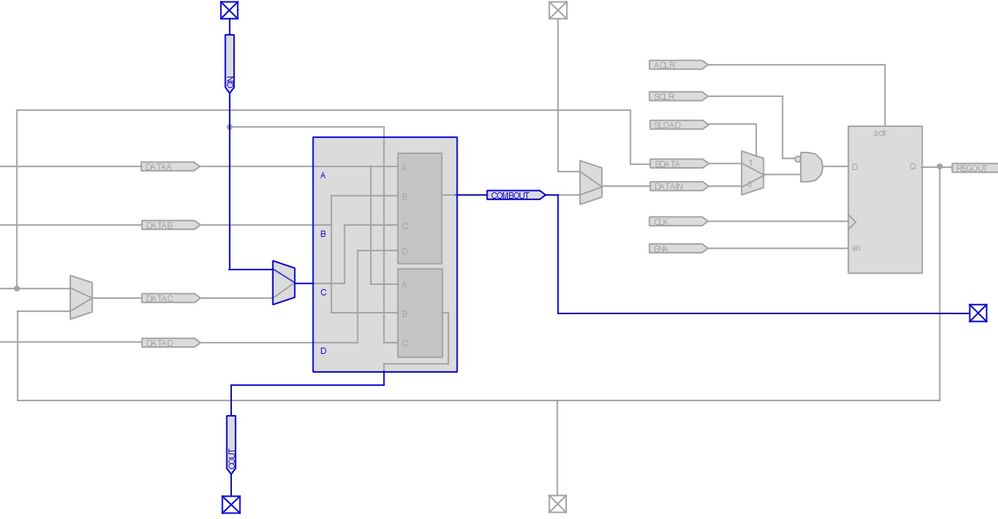

For example, the problem occurs after deleting the last cell in region 0, and the first cell in region 1. I want to connect them directly through carry chain. I guess the problem is not with LogicLock itself, but with the principles of the LE structure.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you share how do you perform the below changes steps by steps in details including the cell name, signal name and node name?

I need each adder to be connected via Cin / Cout carry chains and not through Combout / DataABCD.

As a result of the corrections in the Resource Property Editor, I delete the LEs that work in normal mode and connect each LAB through the carry chains.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

1) I delete the last LE from Region0 "result_int[15]~30"

2) I delete the first LE from Region1 "result_int[0]~1"

3) I connect the COUT of the penultimate LE from Region0 "result_int[14]~29" to the CIN of the second LE from Region1 "result_int[1]~3"

As a result, I want to get two adders connected only by a carry chain

To do the above operations, you can run the updated script.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes. You are correct. The logic lock region assignments are removed when the nodes in a carry chain assigned to a logic lock region is assigned to some of the nodes in a carry chain in another location. To place the carry chain correctly, the Fitter removed the Logic Lock region assignments on the nodes in the carry chain.

Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page