- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sir/Madam,

Quartus prime pro 17.1 + Modelsim 10.5c +Arria10gx

I generated an Intel FFT ipcore from Quartus, I can see some files have been generated under the tfft_17_1_0_240_restored\ft\sim\mentor\

like msim_setup.tcl , modelsim.ini, ,but I have not found testbench relevant file like fft_tb.v, which supposed to be generated automatically.

Many years ago, I use old version fft with old device, I did remember testbench fft_tb.v and relavant real and image txt files also generated automatically.

Is there some updating ? Does FFT IP stop generate those files?

Any suggestion is welcome

Jim

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As you mentioned this was many years ago, the IP may have been upgraded along the way.

Rest assured, in order to generate a simulation testbench, in the IP parameter editor, click Generate > Generate Testbench System. Specify testbench generation options, and then click Generate. A testbench directory will be generated.

You can refer to this page for further details.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qpp-platform-designer.pdf#page=70

-----------------------------------------------------------------------------------

p.s. Don’t forget to Reply, and Select the Best Solution. :)

-----------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ShYanYewT,

Thanks for your support.

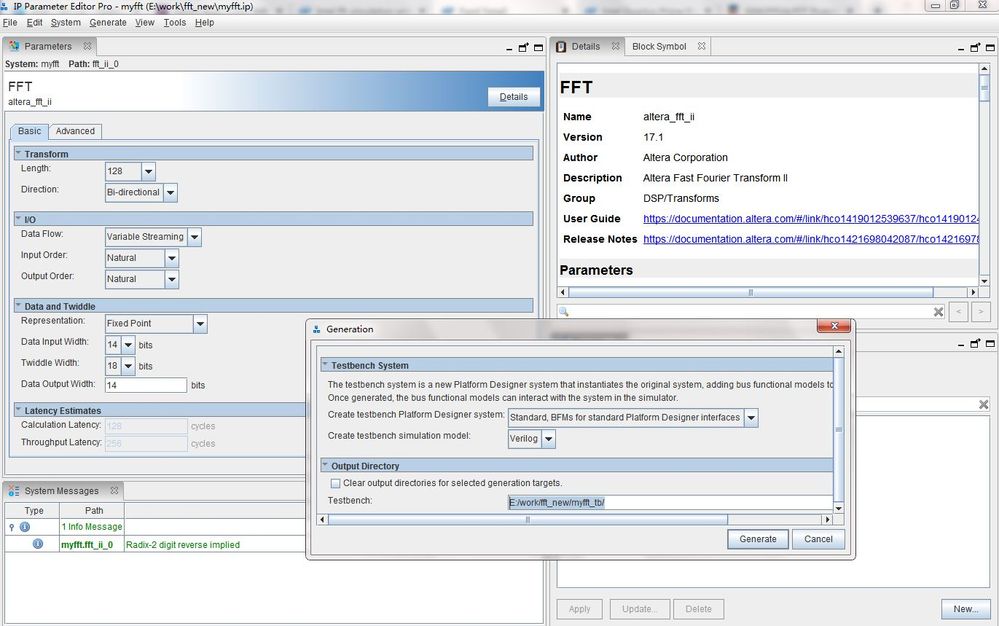

With your suggestion ,I go back to IP setting page and click menu generate->Generate testbench system ,and then

a testbench generation GUI came out , I choosed standard BFM , Verilog MODEL, and output directory is E:/work/fft_new/myfft_tb/

and then click button generate, I can see many files been generated under my nominated location .

I can find the E:\work\fft_new\myfft_tb\myfft_tb\sim\myfft_tb.v , which is the file I mentioned early in last question.

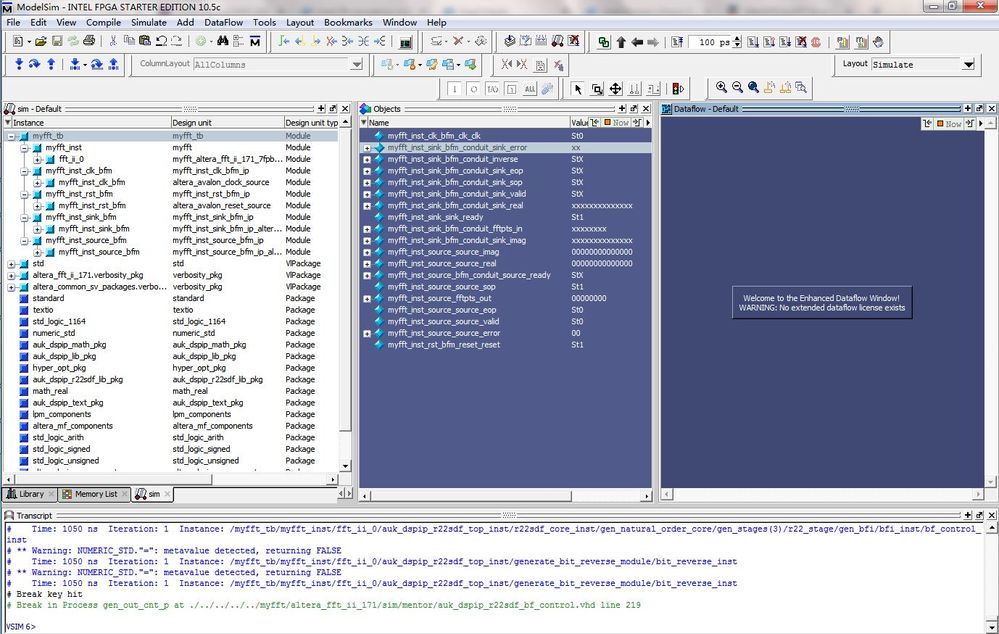

And then start Modelsim-Intel modelsim 10.5c and change directory to

E:\work\fft_new\myfft_tb\myfft_tb\sim\mentor

1,source tcl msim_setup.tcl

2, ld

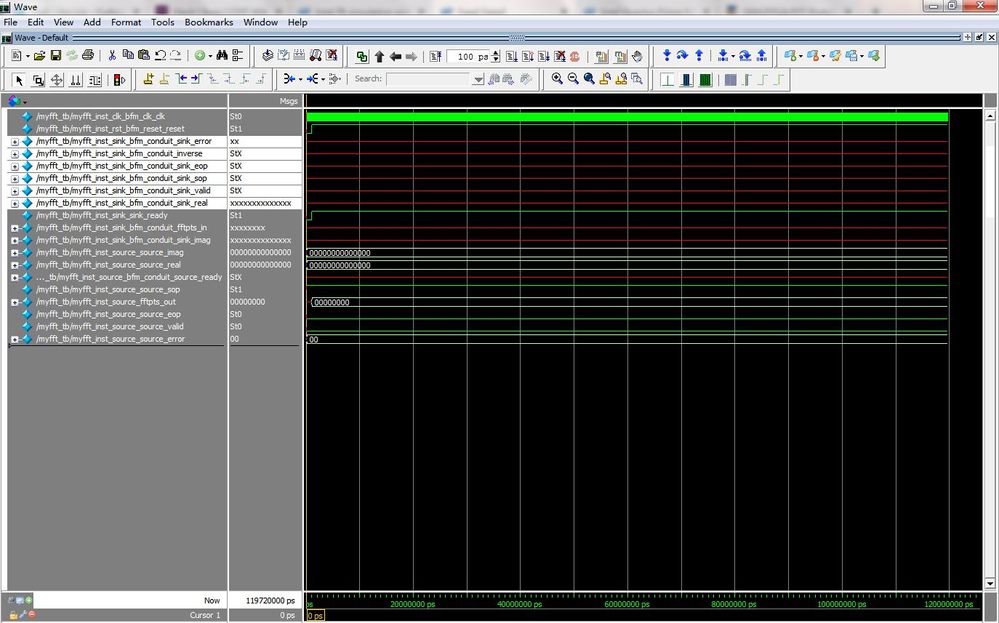

3, manually add top level signals of testbench into waves window , before this step was done by auto-generated tcl ,

4,run –a

5,check the waveform, I can see the clk and rest_n are working as I expected, but BFM part is not working for some reason.

I have not modify any generated files, all of them are generated by tcl.

Id can be performed successfully ,which means device library and ip library have no issue to be compile.

Is there anything wrong? Or I missed out some steps?

I attached 3 picturs anf my project QAR for reference.

Any suggestion is welcome

thanks

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As long as the IP core simulation involves the following steps, you should get it right.

1. Generate simulation model, testbench (or example design), and simulator setup script files.

2. Set up your simulator environment and any simulation scripts.

3. Compile simulation model libraries.

4. Run your simulator.

Those are top-level files, you need to add your own stimulus to it.

For bfm simulation, you can try out the design example below and the document below.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ShYanYewT,

Thanks for your support.

I have check the testbench generated by IP tools, I am pretty believe that testbench has installed all the modules

1, clk_bfm ,use to generate clk output

2, _rst_bfm, use to generate reset output

3, sink_bfm, with clk and reset 2 signal inputs and generate all the sink signals feed to fft IP core

4, source_bfm, with clk and reset 2 signal inputs and generate all the source signals for receiving the fft IP result from FFT IP.

I am not sure what kind of stimulus logic does customer need to add into this fully assembled testbench?

from the error information ,I guess it is just a sink and source BFM wrongly behaved.

but clk and rst BFM are working well.

Thanks

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay in response. I checked and you can generate an fft example design testbench for arria10 but it is only available in Quartus Standard version. Pro version does not generate example design. You can try it out using the example design generated in the standard version.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page