- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

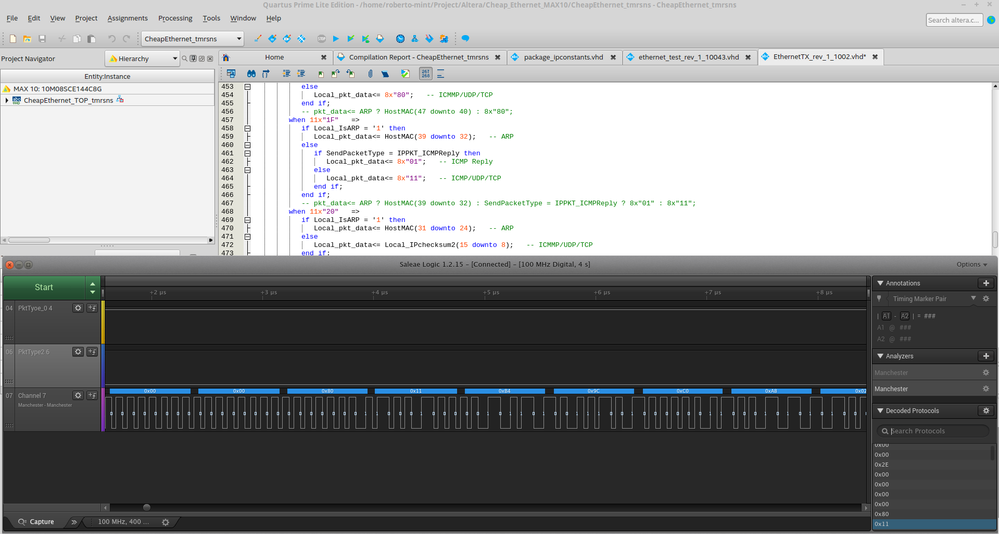

I am trying to convert an Open Core from Verilog to VHDL, doing this I converted one to one modules then cheked them till code work by step.

After last packet conversion, (transmit logic) I seen a strange behaviour, If condition then .. elsif (not true)

execute elsif statement also if not true, is this correct and am wrong interpreting if syntax or quartus version s wrong?

I am observing a lot of strange errant on my IP cores...

packet type is this case (LA checked) UDP, so it must respond 0x11:

this code load paket data with val x11

if Local_IsARP = '1' then

Local_pkt_data<= HostMAC(39 downto 32); -- ARP

else

if SendPacketType = IPPKT_ICMPReply then

Local_pkt_data<= 8x"01"; -- ICMP Reply

else

Local_pkt_data<= 8x"11"; -- ICMP/UDP/TCP

end if;

end if;this code load paket data with val 01

if Local_IsARP = '1' then

Local_pkt_data<= HostMAC(39 downto 32); -- ARP

elsif SendPacketType = IPPKT_ICMPReply then

Local_pkt_data<= 8x"01"; -- ICMP Reply

else

Local_pkt_data<= 8x"11"; -- ICMP/UDP/TCP

end if;Packet type is set to UDP or 01

constants are here:

--- *** ***** **** **** *** *** *** -------------

-- USAGE --

--- *** ***** **** **** *** *** *** -------------

--library work;

--use work.package_ipconstants.all;

--- *** ***** **** **** *** *** *** -------------

library ieee;

use ieee.std_logic_1164.all;

-- Package Declaration Section

package package_ipconstants is

-- constant c_PIXELS : integer := 65536;

-- Packet Types

constant IPPKT_Unknown : Std_logic_vector(2 downto 0) := 3x"0";

constant IPPKT_UDP : Std_logic_vector(2 downto 0) := 3x"1";

constant IPPKT_ARPReq : Std_logic_vector(2 downto 0) := 3x"2";

constant IPPKT_ARPReply : Std_logic_vector(2 downto 0) := 3x"3";

constant IPPKT_ICMPReq : Std_logic_vector(2 downto 0) := 3x"4";

constant IPPKT_ICMPReply : Std_logic_vector(2 downto 0) := 3x"5";

-- constant IPPKT_new : Std_logic_vector(3 downto 0) := 3x"0";

--// Commands

constant IPPKT_CmdDone : Std_logic_vector(7 downto 0) := 8x"0";

constant IPPKT_CmdStatus : Std_logic_vector(7 downto 0) := 8x"1";

constant IPPKT_CmdLEDCtrl : Std_logic_vector(7 downto 0) := 8x"2";

constant IPPKT_CmdSetConfig : Std_logic_vector(7 downto 0) := 8x"3";

constant IPPKT_CmdSwChanged : Std_logic_vector(7 downto 0) := 8x"4";

constant IPPKT_CmdDataEcho : Std_logic_vector(7 downto 0) := 8x"5";regards

Roberto

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

about this I can save and post on Saleae LA file format, it is huge so I do it on demand.

Regards

Roberto

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Try to compile your design and simulate it in Modelsim. This way, you can see if the code is written in the correct way.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank for answer, I spent a lot of time to figure what was wrong, this is a long long time ago flash about.. Hmmm A competitor rewrote old Unix workstation code with M$ tools .. COde was creating a lot of similar mess, input where output and signal not coherent. At last solved with some hack then changed CPLD firm on mass production... They rewrote their tool M$ free.

Why "try" to compile? On release 15.0 of Quartus every IP core was fine, new Linux version are slower.

Current 18.1 Release compile fine, then and elsif selector are both false but result are as elsif true.. Is LRM no more valid or i was wrong for a long time?

I never try see windows version, TOOO SLOW and unreliable.

if elsif elsif end if seems as it is ok.

if elsif else endif seems errant.

TO avoid this I changed structure to nested or case selection.

I cannot rewrite all IP core if this is a tool failure.

I MUST rewrite if I am wrong.

So which one s the offending?

LRM section 8.7 If statement

An if statement selects for execution one or none of the enclosed sequences of statements, depending on the value of one or more corresponding conditions.

if_statement ::=

[ if_label : ]

if condition then

sequence_of_statements

{ elsif condition then

sequence_of_statements }

[ else

sequence_of_statements ]

end if [ if_label ] ;

If a label appears at the end of an if statement, it must repeat the if label.

For the execution of an if statement, the condition specified after if,and any conditions specified after elsif, are evaluated in succession(treating a final else as elsif TRUE then) until one evaluates to TRUE or all conditions are evaluated and yield FALSE. If one condition evaluates to TRUE, then the corresponding sequence of statements is executed; otherwise, none of the sequences of statements is executed.

Best regards.

Roberto

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you create a snippet of code with the design that able to compile? Attached the design.qar here so that I can look into it and get back to you. A simple design will do since it only involve ifelse statement.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

code now is compiled removing elsif, old file still is on HDD, this is an Ethernet 10Base T module, now it is working, as I wrote.

Where can you host my code? This run on proprietary board with RJ45 magnetics and protection, normally is not used on Ethernet but proprietary biphase manchester at higher speed, this is not shareable.

This module got addressed to have a direct fast debug tools due to reduced pin count on device and consquently trouble to use internal/external Logic Analyzer.

The two code snippet on top are the trouble, it generate packet identifier, it is an UDP but is treated as ICMP reply.

Constants are for sure set to 1 not 5, development board has a lot of free pin where I connected the LA probe, Saleae has limit on decoding Manchester when more than 3 input get used but I used Agilent too and I confirm the trouble.

Code where it fail is a rudimental state machine driven by a counter, counter work, using original Verilog module it work, using new pathced module work.

Please give me some time to review old errant module to be compiled on and I send. I have to leave office now, I return back in two hour then I try post code and some images of board, one board is closed, the other can be freely shared with schematics too.

How large can be attached file? I am not ready now to publish back on Open IP Core.

Regards.

Roberto

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Its fine, you can send the design using email. One things is that can you check what is your VHDL version that you were using? Are you using VHDL 2008?

The settings is in assignment -> settings -> compiler settings -> VHDL input

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page