- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The Avalon document mentions waitrequestAllowance parameter but I cant see a way to set it in either Avalon mm bridge or EMIF Avalon interfaces.

How can I set it to 1 for EMIF Avalon interface?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

" waitrequest will usually only be ...". There is no usually in RTL. There is always. So waitrequest may be asserted DURING the burst. This means everything connected to waitrequest must be combinatorial, and can't be pipelined.

Thanks for the help. You may close this ticket.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Interface properties like that are usually for when you create a custom component that makes use of that property. It may or may not be available as a parameter for an off-the-shelf IP. If it's not in the parameter editor, it's not available for customization.

What are you trying to accomplish? Perhaps there's an alternate way to do it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to avoid combinatorial waitrequest signal handshaking between the ddr IP and the user logic .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If you're using Platform Designer, you don't really have a choice in the matter. waitrequest is a required signal for the Avalon standard and required by PD on the host side.

If you are instantiating the EMIF directly in your Quartus project, it does not need to have the Avalon wrapper.

Did you try creating an example design from the EMIF parameter editor to see what this type of connection between user logic and the controller can look like?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

May I know if your question has been answered?

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No it is not.

I said " avoid combinatorial waitrequest", not "avoid waitrequest".

But I did dig in to the code and found out waitrequestAllowance is not supported by Intel EMIF interface claiming it has Avalon interface but not complying on this setting.

Please read the definition of waitrequestAllowance and why it is needed for before answering .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Maybe you can share the issue that you're facing why simulating the design?

Thank you.

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

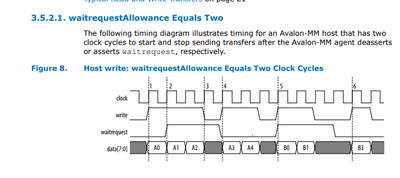

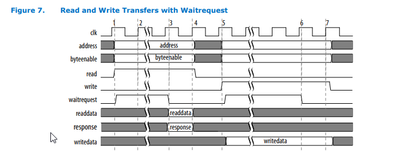

I need tis at the EMIF user interface:

instead of this:

Avalon® Interface Specifications

Updated for Intel® Quartus® Prime Design Suite: 20.1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Alright, I understand on what you're trying to do.

But the waitrequestAllowance signal is the internal setting hardcoded in EMIF IP that shouldn't be touched by user.

Changing this signal might cause functionality failure in the EMIF IP.

Have you tried the burst operation?

If you want to optimize the controller performance, you can refer to EMIF User Guide for the device that you used.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I did not ask for touching internal settings of EMIF. I asked if EMIF supports waitrequestAllowance parameter for the user. And I found out looking into EMIF code that the answer is no. There is no such thing in the code but instead a ready signal is inverted to create the waitrequest signal.

I am already using burst operation. But there is no explanation for waitrequest will not be asserted during burst. Can you tell that When burst start, waitrequest will not be asserted until the end of the burst?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

waitrequest back to your user logic is handled by a combination of the signal coming from the agent (the EMIF IP) and the interconnect (usually for arbitration purposes but any time the agent can't currently accept a command).

If you initiate a burst and then waitrequest to your user logic goes high, that means your logic (host) gets access to the agent until the burst completes. As the Avalon spec shows (figure 14 and 15 in the latest version of the doc), for a burst, waitrequest will usually only be asserted at the beginning of the burst or whenever the interconnect (or agent) requires the host to continue asserting the control signals for some reason (typically arbitration).

I think this is why Adzim suggested using bursts, since waitrequest isn't held high throughout them.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

" waitrequest will usually only be ...". There is no usually in RTL. There is always. So waitrequest may be asserted DURING the burst. This means everything connected to waitrequest must be combinatorial, and can't be pipelined.

Thanks for the help. You may close this ticket.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page