- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a module I want to test

out_control.vhd

entity OUT_CONTROL is

port

(

CLK : in std_logic;

RST : in std_logic;

OUT_MASK : in std_logic_vector(55 downto 0);

OUT_ON_OFF : in std_logic_vector(55 downto 0);

OUT_TRIG : in std_logic;

OUTPUTS : out std_logic_vector(55 downto 0)

);

end entity OUT_CONTROL;

architecture behavior of OUT_CONTROL is

type OutStateType is (ST_IDLE, ST_SET);

signal OutState : OutStateType := ST_IDLE;

begin

process(CLK)

begin

if (rising_edge(CLK)) then

case OutState is

when ST_IDLE =>

if (OUT_TRIG = '1') then

OutState <= ST_SET;

end if;

when ST_SET =>

for i in 0 to 55 loop

if (OUT_MASK(i) = '1') then

OUTPUTS(i) <= OUT_ON_OFF(i);

end if;

end loop;

OutState <= ST_IDLE;

when others => OutState <= ST_IDLE;

end case;

end if;

end process;

end behavior;And a test bench

out_control_tb.vhd

entity out_control_tb is

end entity;

architecture test of out_control_tb is

component OUT_CONTROL is

port

(

CLK : in std_logic;

RST : in std_logic;

OUT_MASK : in std_logic_vector(55 downto 0);

OUT_ON_OFF : in std_logic_vector(55 downto 0);

OUT_TRIG : in std_logic;

OUTPUTS : out std_logic_vector(55 downto 0)

);

end component;

signal reset : std_logic := '0';

signal clock : std_logic;

signal s_out_mask : std_logic_vector(55 downto 0);

signal s_on_off : std_logic_vector(55 downto 0);

signal s_outputs : std_logic_vector(55 downto 0);

signal s_out_trig : std_logic;

signal stop : boolean;

begin

U_OUT_CONTROL : OUT_CONTROL

port map

(

CLK => clock,

RST => reset,

OUT_MASK => s_out_mask,

OUT_ON_OFF => s_on_off,

OUT_TRIG => s_out_trig,

OUTPUTS => s_outputs

);

clkgen : process

begin

while true loop

clock <= '0';

wait for 10 ns;

clock <= '1';

wait for 10 ns;

end loop;

wait;

end process;

process

begin

if (rising_edge(clock)) then

wait for 100 ns;

s_out_mask <= X"0000000000000F";

s_on_off <= X"0000000000000F";

s_out_trig <= '1';

wait for 20 ns;

s_out_trig <= '0';

s_on_off <= X"00000000000003";

s_out_trig <= '1';

wait for 20 ns;

s_out_trig <= '0';

wait;

end if;

end process;

end architecture;

Now I do

1. open a new project in Modelsim

2. add files out_control.vhd and out_control_tb.vhd

3. compile files successfully

4. Simulation -> Start Simulation -> select work/out_control_tb.vhd

5. Add signals to a Wave view.

6. Press Run ( Run continuous) button.

I see

VSIM 23>run (VSIM 24>run - continue)

And nothing. No signals appear on the Wave tab.

What do I do wrong?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think you have to say run -all to advance the simulation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

Do you have any update on your problem?

Thank you

Regards,

Ean

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well...Some problems I resolved another pop up.

For example

process

begin

reset <= '1';

wait for 100 ns;

reset <= '0';

wait until s_send_rdy = '1';

s_send_data <= X"88";

s_send_trig <= '1';

wait for 40 ns;

s_send_trig <= '0';

wait until s_send_rdy = '0';

wait until s_send_rdy = '1';

s_send_data <= X"ED";

s_send_trig <= '1';

wait for 40 ns;

s_send_trig <= '0';

wait until s_send_rdy = '0';

wait;

end process;

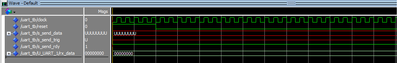

And I see

Is wait until working directive?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

wait until doesn't exist in Verilog. Quick Google search for a replacement:

https://stackoverflow.com/questions/12370324/verilog-equivalent-of-wait-until-for

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Who is talking about Verilog ???!!!

Where do you see a single line of Verilog in my code ???!!!

Jesus Christ!!! Unbelievable!!!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page