- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm attempting to implement simple power sequencing logic in a MAX10 fpga.

There are four groups of power regulators that are enabled sequentially when the each regulator in the preceding group supplies a "good" signal.

I get warnings that my "PGOOD_*" inputs are not driving logic, and that my "ENABLE*" outputs are stuck at VCC or GND.

This doesn't make sense to me because these inputs are being sent into my "power_sequencer" submodule where they trigger state machine transitions. For specific states in this submodule outputs are activated that are routed back up to the top-level "ENABLE*" outputs.

When I look at the RTL viewer everything looks okay, but post fitting those inputs go nowhere. Why is my design being optimized away?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Weird. Other things I notice: you have 6 states, but you set S_FSM_ERROR as 'x (and only using 5 bits for the state). It should probably have a defined value. Also, even though you are manually doing one-hot encoding here, did you create a state machine encoding assignment in the Assignment Editor?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Your clock naming is mismatched. In the top-level port mapping, you call the clock ip_clk_25 but in the power sequencer, it's call ip_clk.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes. I introduced this mistake before posting. Unfortunately it is not the cause of my issue.

Even with this mistake fixed my logic is being optimized away.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Something to try: normally for a state machine, you use two separate processes: a clocked process for the next state logic and a combinatorial process for the outputs. Because you've combined these and you are using non-blocking assignments for what should be combinatorial logic, it's possible the outputs are not getting updated as expected. Try separating out the processes.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I can try that, but I haven't had an issue combining state and output logic in the past. When I simulate the design as-is the logic works fine.

(hopefully this snapshot is readable when uploaded)

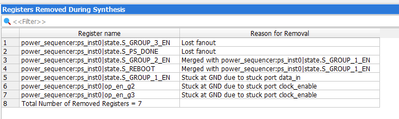

Under optimization results I see:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Weird. Other things I notice: you have 6 states, but you set S_FSM_ERROR as 'x (and only using 5 bits for the state). It should probably have a defined value. Also, even though you are manually doing one-hot encoding here, did you create a state machine encoding assignment in the Assignment Editor?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This paper (http://www.sunburst-design.com/papers/CummingsSNUG2019SV_FSM1.pdf) also makes use of a don't care state to account for the unused states in the typedef state enumeration. I have used this coding style before without issue.

I'm unfamiliar with creating a state machine encoding assignment, but I do know that a state machine is being inferred by this code as it appears as designed in the "Analysis and Synthesis - State Machine" output.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It turns out that my issue was caused by using 'x in my typedef state enum after all.

Something must have changed, or this project's settings are slightly different in some way because I have used this construct successfully before.

typedef enum logic [4:0] {

S_REBOOT = 5'b0_0001,

S_GROUP_1_EN = 5'b0_0010,

S_GROUP_2_EN = 5'b0_0100,

S_GROUP_3_EN = 5'b0_1000,

S_PS_DONE = 5'b1_0000,

S_FSM_ERROR = 'x <-- Removing this fixed my issue.

} state_e;

state_e state;

I then decided to add in another state for error catching (the default case switch sends the FSM to this state) and let the compiler assign enum values automatically:

localparam STATE_NUM = 6;

typedef enum logic [STATE_NUM - 1 : 0] {

S_REBOOT,

S_GROUP_1_EN,

S_GROUP_2_EN,

S_GROUP_3_EN,

S_PS_DONE,

S_FSM_ERROR

} state_e;

state_e state;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Create a "State Machine Processing" assignment in the Assignment Editor and set the encoding style appropriately.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I added the "State Machine Processing" assignment, but am still seeing the issue.

I think a big part of my problem is that the project doesn't think that "Clock_25MHz_Max10" or "RESETn" have outputs that are dependent on them. I've tried using "Clock_25MHz_Max10" directly by bypassing the PLL. I've tried adding "set_instance_assignment -name GLOBAL_SIGNAL GLOBAL_CLOCK -to "Clock_25MHz_Max10" " into my .qsf.

Could the .sdc cause this isue?

At the moment I have an .sdc that has:

set_time_format -unit ns -decimal_places 3

create_clock -period 40 [get_ports Clock_25MHz_Max10]

derive_pll_clocks

derive_clock_uncertainty

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page