- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi guys

I wanted to ask if there's a possibility to either pass a generic/constant argument to qsys IP or make the defined generic/constant available.

The idea is to define the value of an SPI clock speed only at one place and everything else follows suit. Right now we just instantiate a standard IP block and set the value manually and there's another VHDL file that also utilises the SPI but doesn't know the SPI clock speed resp. we need to manually define it which could be theoretically forgotten if someone changes the value in qsys.

I appreciate any replies and wish a nice time.

Kinda regards

Luigi

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Are you saying this is a parameter set in a standalone IP that you want to transfer into a lower-level (instantiated) Platform Designer system?

Or are you saying this is a component already in a PD system that you want to want to pass its parameter value elsewhere in the system (hierarchical system design)?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

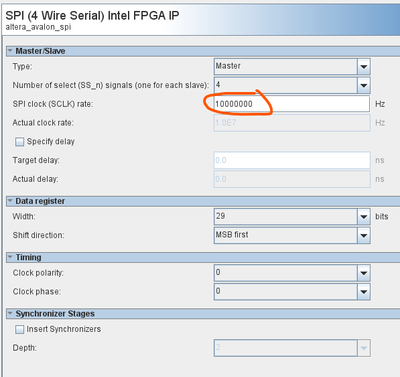

The parameter is set in an IP (4-line SPI) that you can generate with qsys. It's a standalone IP, I'd guess.

My aim is to set this parameter either via a generic that can be generated in 'HDL parameters' (see: https://www.intel.com/content/www/us/en/docs/programmable/683609/21-3/exporting-hdl-parameters-to-a-system.html) or I make this value I set in the given screenshot to other VHDL modules available. It's just to avoid one source for potential mistake.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You can export as HDL parameter. Then pass the generic with the command set_parameter check this link https://www.intel.com/content/www/us/en/docs/programmable/683432/22-4/tcl_pkg_project_ui_ver_1-0_cmd_set_parameter.html or using GUI by go to Assignments -> Settings -> Default Parameters

Thanks,

Best Regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sry for late response. I tried it out. However, I don't see how I can pass this parameter from .qsf file to the IP module or take the value from the IP module. Maybe, I'm missing the connection here somewhat.

Kinda regards

Luigi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Luigi,

Just notice that this SPI Intel FPGA IP originally don't have any HDL Parameter so you can't pass this parameter from .qsf file to the IP module or take the value from the IP module.

Possible way is to manually create parameter for the slowcount in spi_spi_0_altera_avalon_spi_1923_przinoa.v check screenshot below and link that parameter all the way to top level wrapper. 128000 Hz having 196 clock pulses while 100000 Hz having 250 clock pulses. However, you probably can only pass this parameter to IP module but can't take value from IP module because that module will be getting changed back to original version when IP being regenerated. So may be you can export system as .tcl and read IP value from .tcl.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good morning Sheng

I see unfortunately that's what I wanted.

Kinda regards

Luigi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Seems like export the system in .tcl and compare, modify the values in .tcl will be more easier. Then use qsys-script command to source it. Then, run qsys-generate or Generate HDL in GUI.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

set parameter -entity xxx -name yyy zz works for me to set VHDL generics.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sure, let me know if you still have any further update or concern.

Thanks,

Regards,

Sheng

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page