- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Platform Designer(Cyclone10GX、Quartus Prime18.1 build222)

にて、以下3種のIPにてシステムを構成しているのですが、

64bitのベースアドレス設定がうまくいきません。

具体的には、64bit設定しても強制的に32bit設定となってしまいます。

※バージョンは異なりますが、CycloneVで同様の構成実績あり

PlatformDesignerのAddress Mapのタブの情報から、CYC5とCYC10では、64bit、32bitのアドレスの扱いが違うようなことはあるのでしょうか?

添付の「cyc10アドレスマッピング問題.xlsx」のCYC10シートの赤丸部をご確認ください。

■目的

Platform Designerシステムにて、

pcie_a10_hip_armmのtxsポートのベースアドレスを

0x0000 0001 0000 0000

としたい。

設定しても反映されない問題があるようです。

【使用IP】

・Intel Arria10/Cyclone10 Hard IP for PCI Express

(Avalon-mm、Native endpointで使用)

・Modular Scatter-Gather DMA Intel FPGA IP(Memory-Mapped to Memory-Mapedで使用)

・On-Chip Mmeory Intel FPGA IP(DualPortRAMで使用)

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Looks like the msgdma only have maximum 64 bits addresses. So, this already fully utilized by the PCIe avalon-mm address width. So, it cannot be share with the on-chip memory.

Or is there any misunderstanding here. Perhaps you can attach the qsys file for further clarification.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ご回答ありがとうございます。

うまく伝えられず、申し訳ありません。

目的は、

Quartusヴァージョンは異なりますが、以前CycloneVを使用して作成したシステム構成と同様なアドレスマップにしたい。

※CycloneVのQsys構成を添付します。

問題点として、

■CycloneV

pcie_a10_hip_armmのtxsポートのベースアドレス:0x0000 0001 0000 0000

⇒設定可能

資料を添付します。

■Cyclone10 GX

pcie_a10_hip_armmのtxsポートのベースアドレス:0x0000 0001 0000 0000

⇒設定不可

64bitのベースアドレス設定がうまくいきません。

以上、宜しくお願い致します。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

Can you zip the Qsys file or full project qar file and upload to here? Also, let me know the Quartus version for the files that you attached 😄

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ご連絡ありがとうございます。

プロジェクトファイルを添付します。

下記にこちらでの設定手順を記載します。

尚、同様な手順でQuartus standard 18.1にてArria10は設定できました。

ご確認の程、宜しくお願い致します。

■手順

1) qarファイルをQuartus Prime Pro ver18.1で開き、projektを作成

2) IPをアップグレード

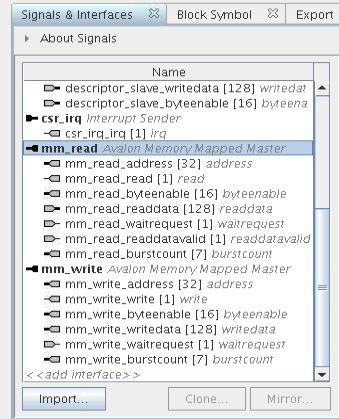

3) Platform Designerにて、pcie_a10_hip_armmのtxsポートのアドレス空間を4GBとしたいが設定できない。

・base address:0x0000 0001 0000 0000

・end address :0x0000 0001 ffff ffff

⇒設定しようとすると、

「Error: pex_avmm_grd.msgdma.mm_write: pcie_a10_hip_avmm.txs (0x0..0x1ffffffff) is outside the master's address range (0x0..0xffffffff)」

のエラーが表示される

以上、宜しくお願い致します。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thanks for the design. I open it and follow the step. I observe the msgdma have and avalon-mm master port with address width 32. This mean the MSB of the address should be ffff_ffff. So, 1_0000_0000 of the txs port is out of the range of this master component. The error is valid.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ご回答ありがとうございます。

Master側のMsgdmaが32bit adressingとなっているのが問題と理解しました。

下記を参照すると、mSGDMAの parameter editorにて、

・ Extended Feature Options

を選択することで64-bit addressing が可能となると理解しました。

https://www.intel.com/content/www/us/en/programmable/documentation/sfo1400787952932.html#lro1402196946061

この認識で正しいでしょうか?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Based on the document, seem like turn on this feature will make the address become 64bits. But its still give me 32 after turn on this feature.

Do you have successful case that can allow you to change the address from 32 to 64? I am asking this because I remember you mentioned that you can set the address 1_0000_0000 in other device family?

Also, may I why you want to set the based address to 1_0000_0000? Usually user will prefer the smaller address which is 0000_0000.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ご連絡ありがとうございます。

結果的に、下記設定で64bit addressingが可能となり、問題は解消されました。

ありがとうございました。

Msgdmaのパラメータ設定にて、

・Enable Extended Feature Supportにチェック

・Use pre-determined master address widthにチェック、64bitに設定

尚、base addressを0x1 0000 0000としたかった理由は、過去の設計資産を流用したかったからです。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir, Thanks for your confirmation. Glad to know that you able to find the way to make the address to 64 bits. At my side, I still waiting clarification from the MSGDMA owner. But now seem like we got the answer.

I'm very sorry for the delay.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page