- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, I have a problem with the Deinterlacer IP Core. I created a video system with the following input chain:

CVI->CLIPPER->COLOR PLANE SEQUENCER->CHROMA RESAMPLE->DEINTERLACER->MEMORY CONTROLLER->DDR3 MEMORY

After I created a Testbench to simulate my system. I send a CVBS interlaced video sequence on CVI input. Looking the waveforms the first frame begins to flow through the IPs and the Avalon Control Packets are correct. When the frame arrives on Deinterlacer input, the Deinterlacer output Avalon Control Packet is correct, but after the Deinterlacer output "din_ready" goes low, blocking the entire video flow. The Deinterlacer lowers the "din_ready" and doesn't send command to the Memory Controller in order to write the frame into memory. What's my problem?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, you seems to observe the din_ready from the Deinterlacer II de-asserts after feeding into video data in simulation. When din_ready is de-asserted, the IP is unable to receive further data.

To facilitate further debugging, would you mind to create a simple test design ie with TPG II -> DIL II (+ memory) -> CVO run with Modelsim simulation. YOu may start with small video resolution ie 100x100 to use on-chip memory to further isolate out the memory controller. Once the simple test design is simulating correctly, you may then slowly replace the component to test out. This would be helpful to narrow down to the root cause.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the response. I followed your advice, but I get the same problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For your information, I have emailed you a simple simulation example design from wiki previously with A10 TPG -> DIL -> CVO, using on-chip memory. You may try with it and then refer to it for your design. This example is created with Q17.0std.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I had already seen that example and it works, but in Deinterlacer is selected the algorithm Vertical Bob. If I start with that example and change the algorithm from Vertical Interpolation to Motion Adaptive, inserting the On-Chip memory, the Deinterlacer doens't work and I get the problem described.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I received your email. The email text is as follows:

A10 simple simulation example with TPG -> DIL -> CVO in Q17.0

ref:_00DU0YT3c._5000Pq1DlN:ref

But I don't see any simulation example. I haven't received the attached file. Could you send me the file again? Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have emailed you a new archive which I further compress the zip. Please let me know if it still cannot get through your email.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

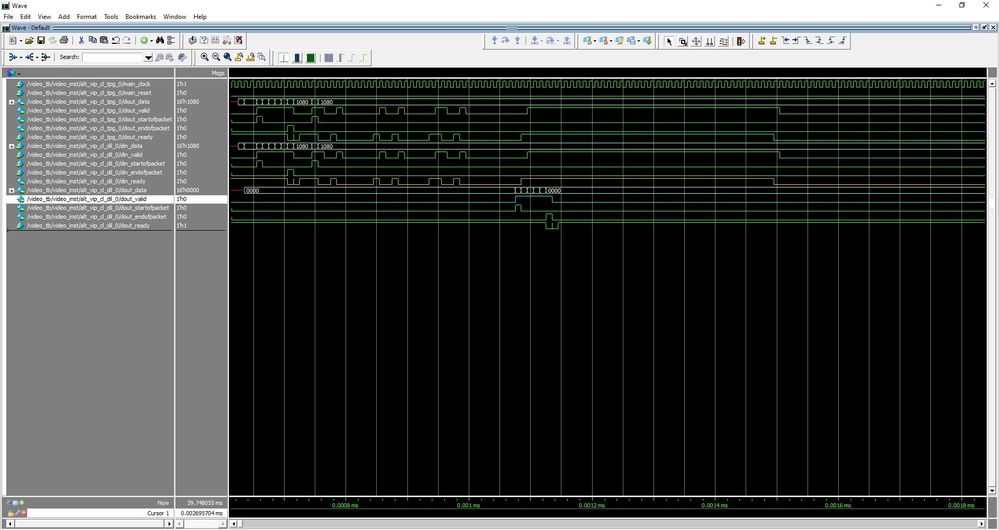

Thank you. I tried your design, but I get always the same problem. I attack the simulation waveforms. As you can see the deinterlacer starts the frame acquisition and sends the control packet with dout_valid (cyan), but after lowes the din_ready (yellow) and stops the frame acquisition. What could be the probem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry I can't see the screenshot. I see "[cid:image007.jpg@01D603A0.DE03CCD0]" , it seems that the image has been not correctly inserted.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the inconvenience. I have resent the screenshot thru email attachment. Please let me know if you are still unable to view it.

thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I received the screenshot. Your waveforms are ok, but when I run the simulation in your zip I get different waveforms. I don't see the din_ready reassert, it always remains low. I can't understand how it's possible, the test bench file is the same. Mabybe depends on the simulator used. I'm using QuestaSim-64 10.6g.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If I use Modelsim it correctly works. Anyway I need use QuestaSim in order to create an UVM testbench. I'll try with an other QuestaSim version.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I resolved my problem. The Deinterlacer with QuestaSim-64 10.6g doesn't work. I installed Questasim-64 10.2c and now correctly works. Thank you so much for your support 🙂

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Glad to hear that you have managed to resolve the issue. Thank you very much.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page