- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

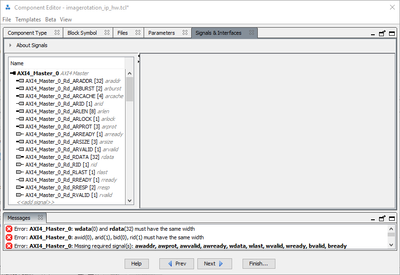

I am using Qsys component editor to package my IP which has an AXI4 Master interface.

My AXI4 Master interface only contains AXI read signals, because I don't use AXI write channel at all.

However Qsys doesn't allow AXI Master interface to have read channel only.

The error message is clear enough to me.

My question is other than creating dummy AXI write signals on my top module, is there any setting to bypass this validation?

I prefer not changing my HDL code. AXI4 Master interface with either write or read channel is not against the protocol anyway.

Thanks!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Peng,

Seem Qsys cannot handle undefined required signal for AXI4. You should declare the list signal in order to error free. What are trying to do with module with only read signal? Handshaking happen seem not proper if that so.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks,

My module will only do axi master read from the downstream. It doesn't perform axi write data to the slave, so there is no point to have axi master write signals in the top HDL. It is a very common design, for example memory map to stream (MM2S) DMA.

My model doesn't have only 'read' signals. As you can see in my attached picture, the module has all read channel signals.

BTW, this module works in Xilinx Vivado. It is just not supported in Quartus.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Peng,

Did you manage to work on this?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page