- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

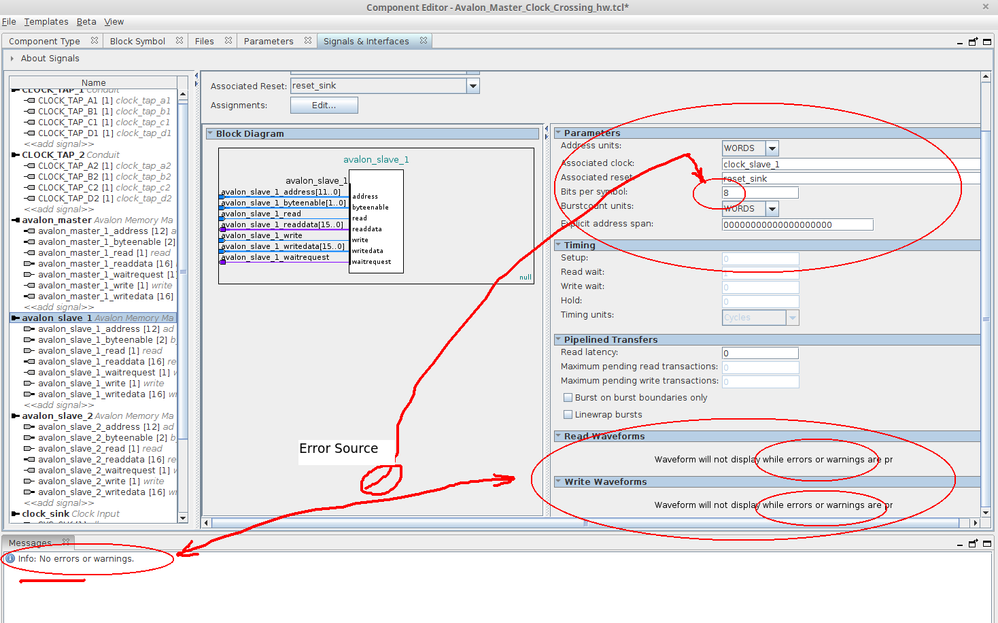

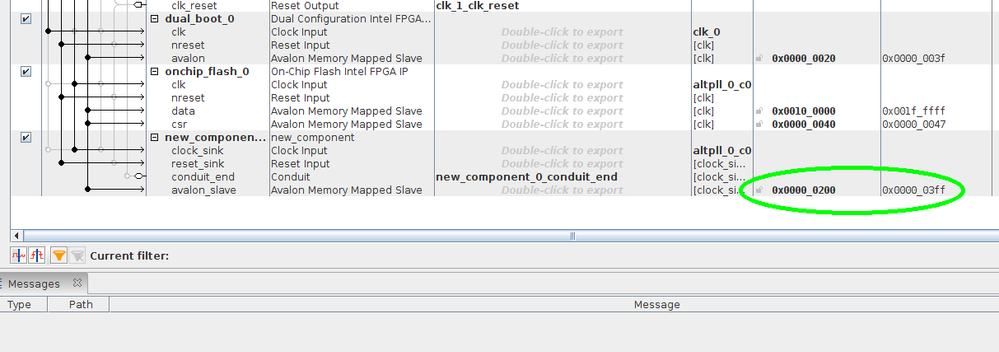

My IP core design, core was not working and error was hidden,

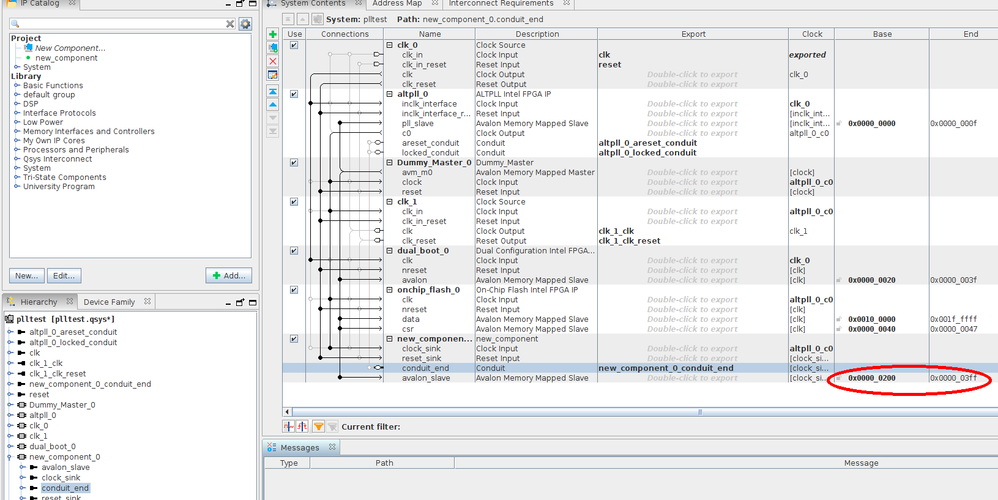

production fabric report component as ok, found debugging memory address was wrong.

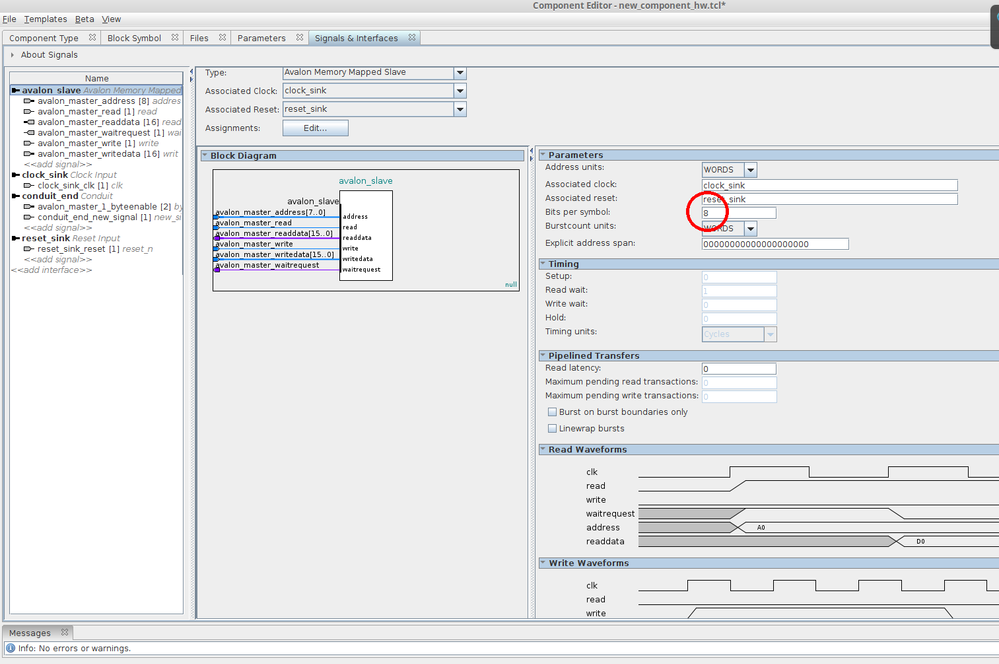

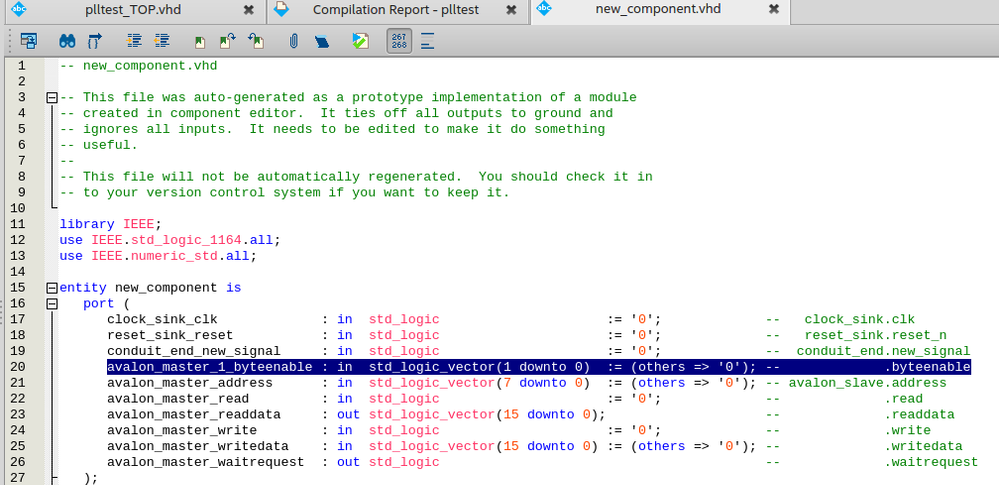

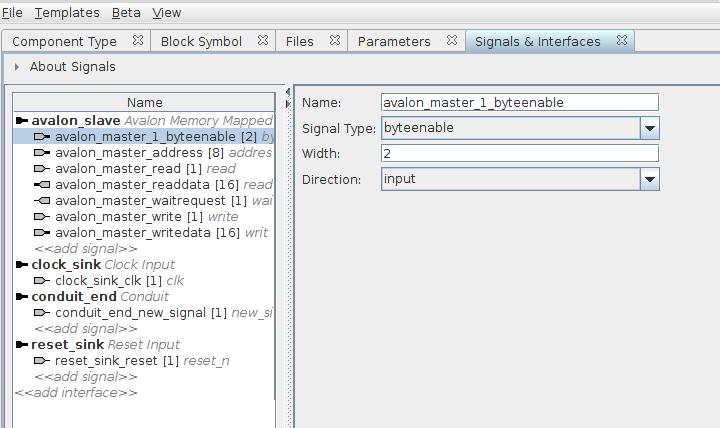

Added missing byteenable was on conduit by error.

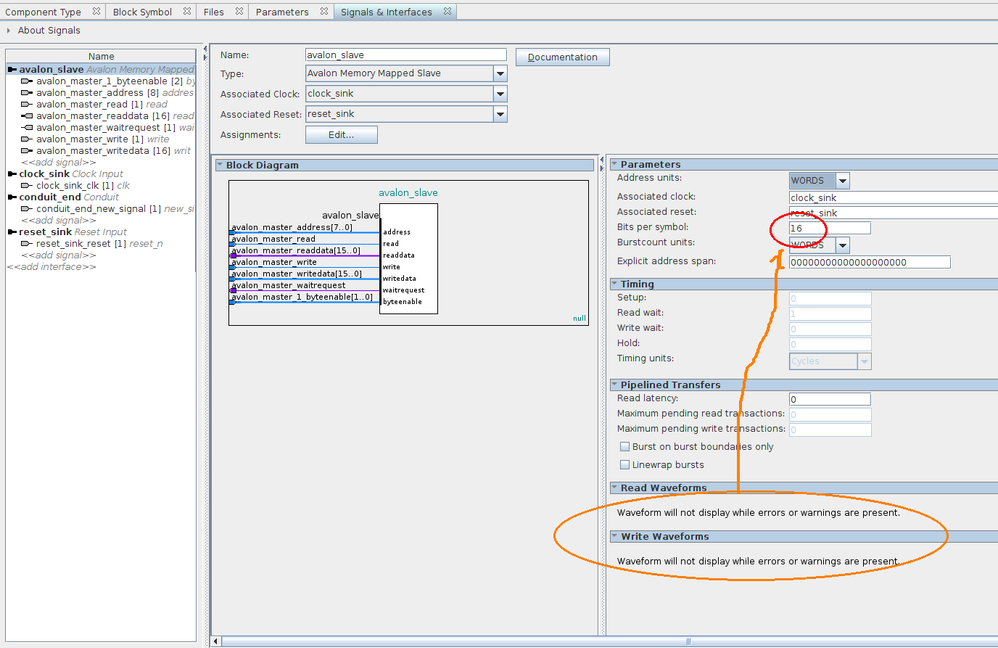

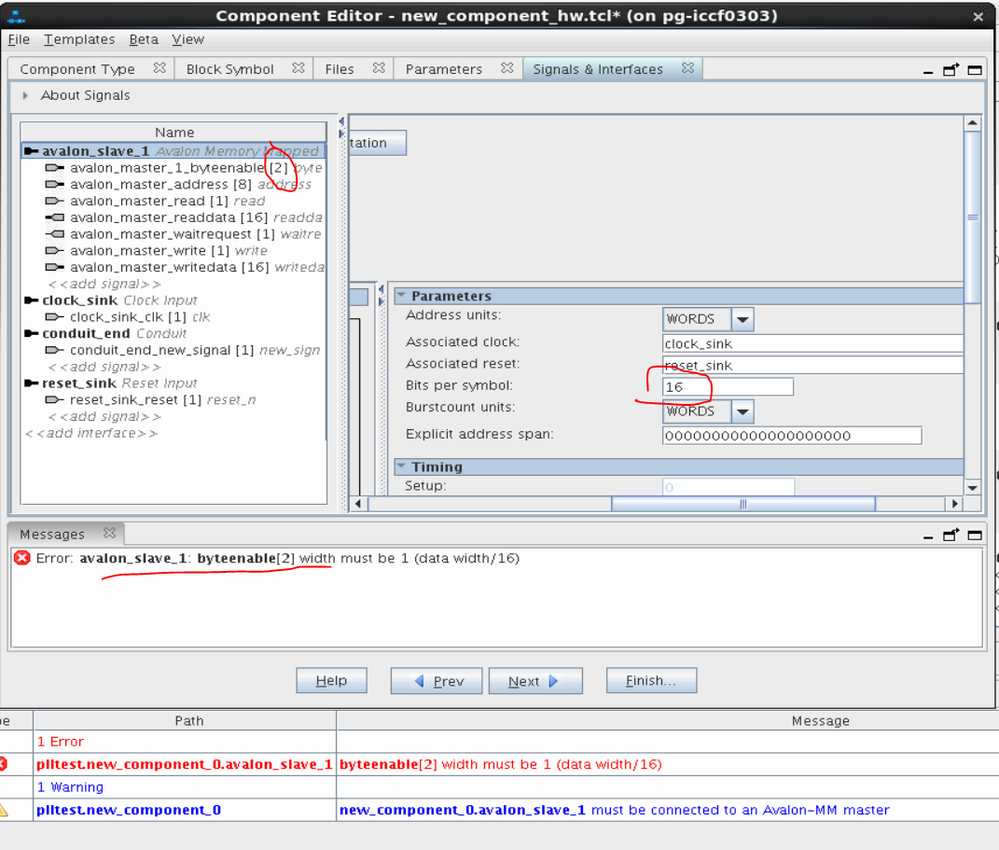

Moving Byteenable to avalon interface generated this uncought, waveform report error and same time module say there where no error.

Avalon bus doesn't show waveform, build without error.

offending parameter, byteenable was added late

byteenable added later then set to 8 bit

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know which version and edition of the software you are using? Could you provide a test case and steps to reproduce the error?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

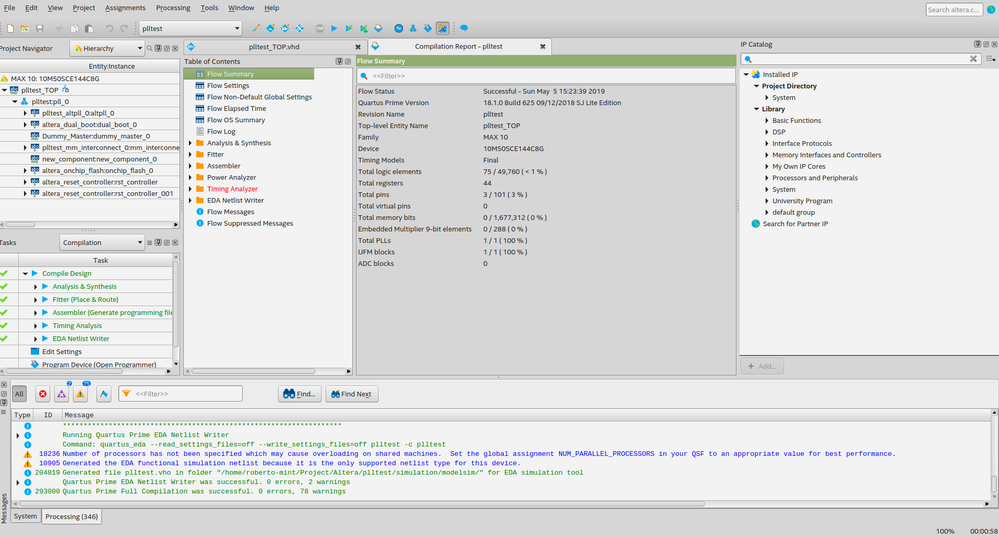

Versionless, both 18.1 and 15.0 where same, I recently removed 16.1 and 17.1.

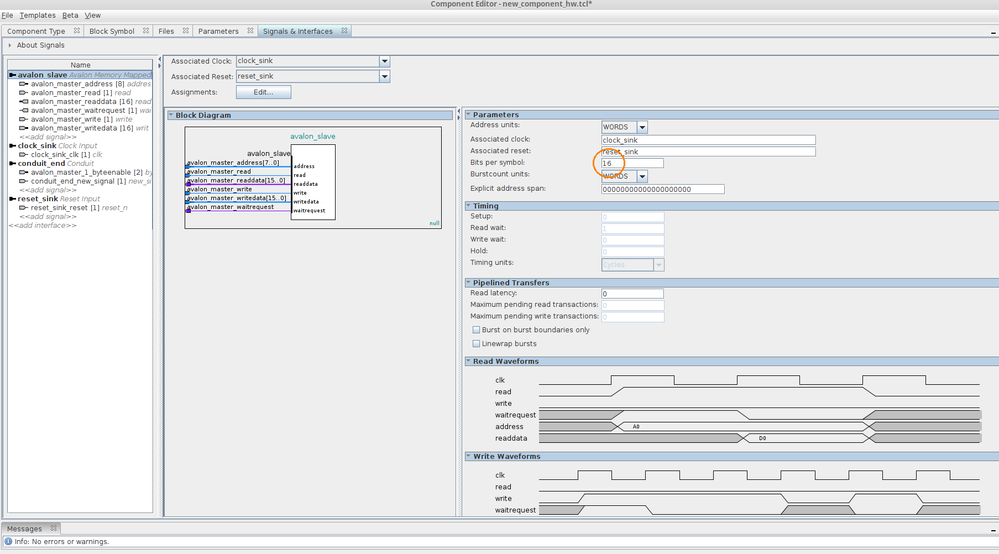

Avalon bus, wrong Symbol size with byteenable size 2 generate wrong Core.

Error is partially captured on waveform but doesn't block code generation.

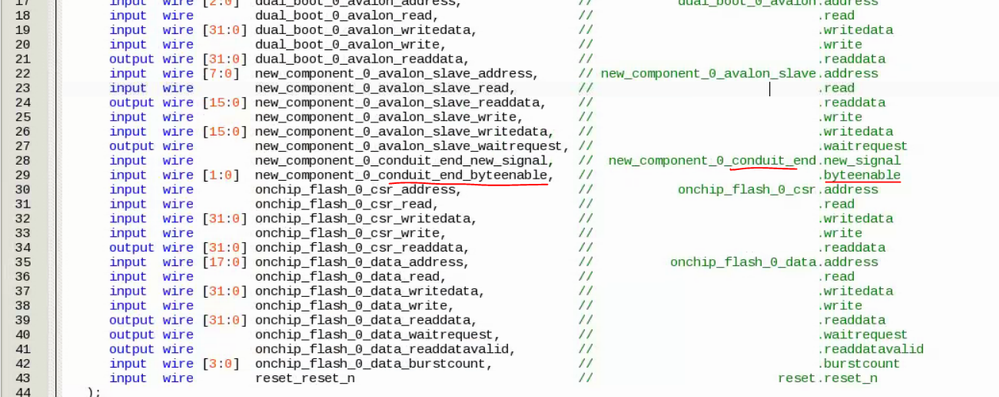

Generating an IP assign all signal but byteenable (reread first post)

moving byteenable from wrong interface produced this error.

If you are not able to reproduce I can build two snippet, this is stable regardless of OS or version.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

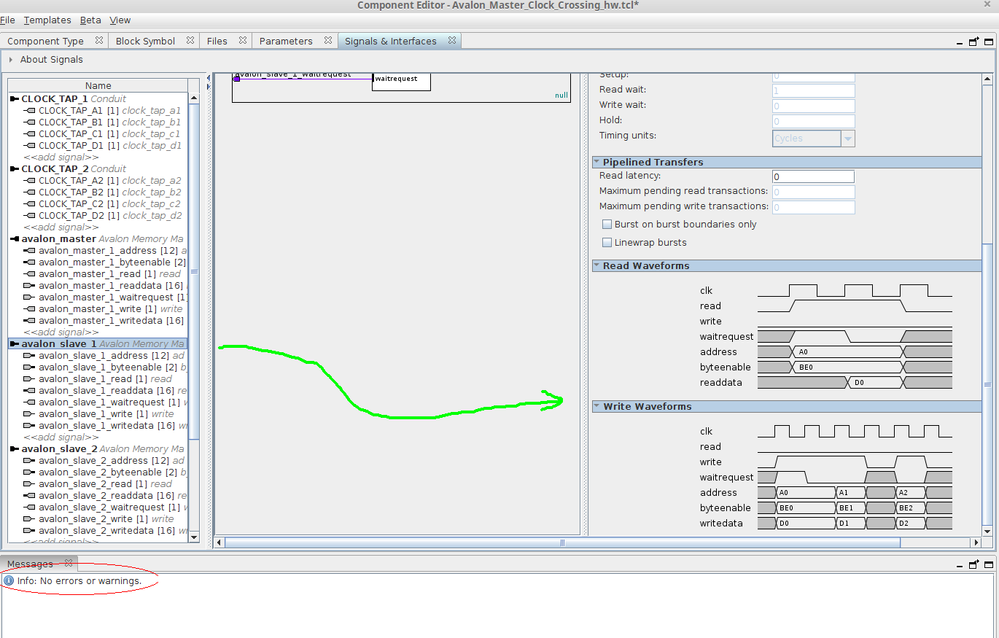

Step to generate wrong model:

Add Avalon Slave signals ( here was QSYS default, my code was written on Quartus editor then assigned.)

Add byteenable after generating Conduit, then move to conduit ( this generated my mess with Qsys, probably selected by mistake then moved to conduit).

changed symbol width. wrong without byteselect, so it map twice to bus elements still 16 bit wide.

Address range look as it is ok

Build say nothing

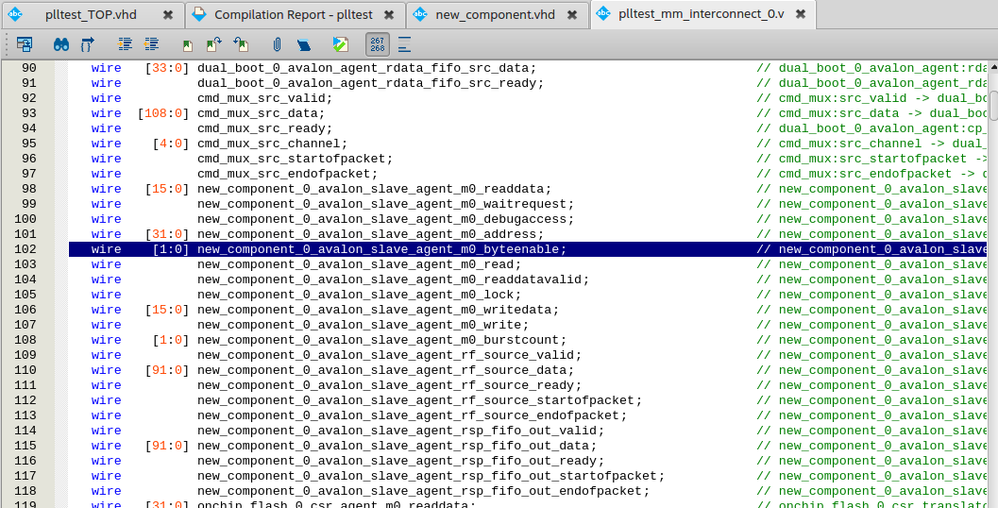

Byteselect is still assigned to bus adapter. (found assigned as "11" (VHDL) or 2b'11 Verilog

VHDL generated look ok (My core was ok so took some time to point out)

Memory got duplicated from odd and even addresses, clearly no selection about byte was present and byte writing was destructive.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

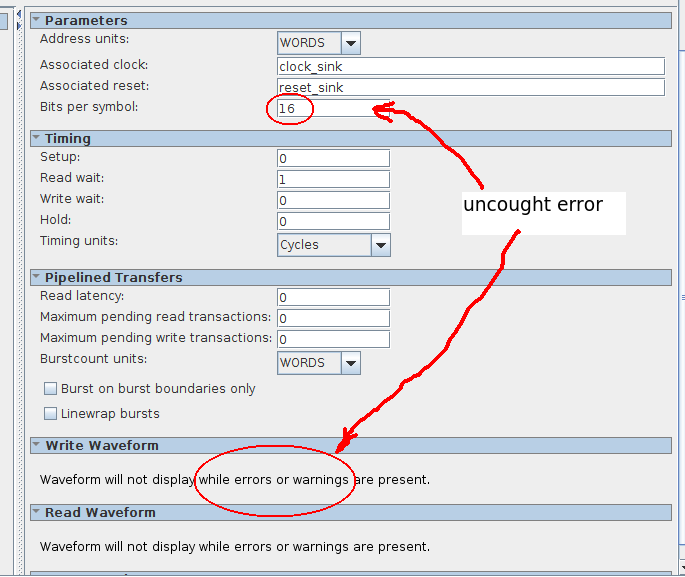

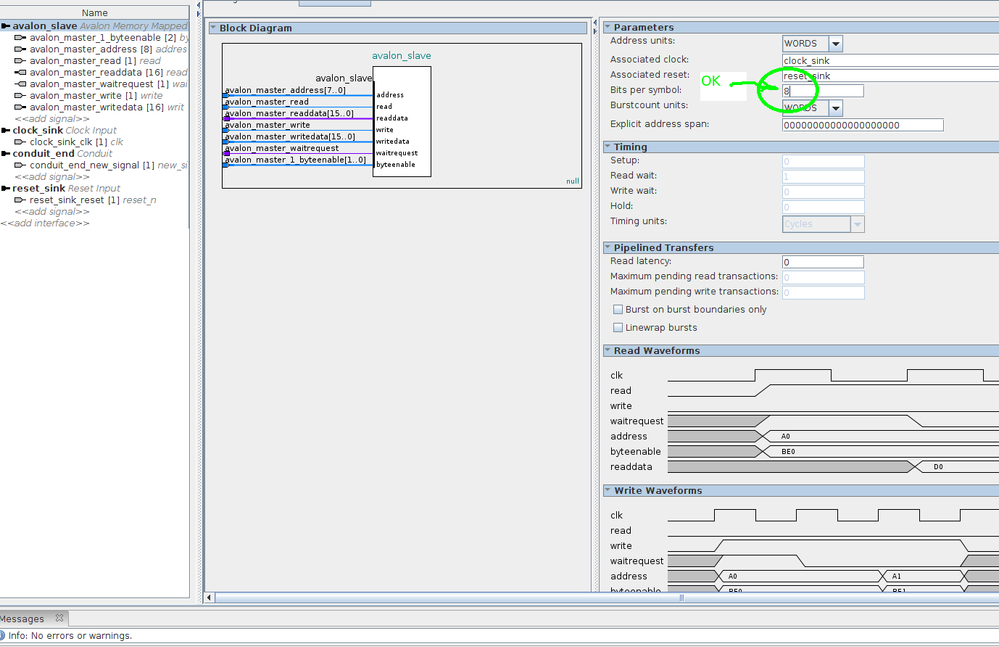

Solve unaddressed issue:

edit IP core(Qsys component):

Select and move to avalon Byteenable

Now Slave interface is complete byte addressable:

Still no error but no wave and error or warning. Yes error is present.

Set to Symbol to right byte size and issue is cured

You can check on both error and correct code where reported as good. Also memory range was reported as good with misaddressed sizes.

Both odd and even word where addressing same word cell.

Here is ok than with wrong signalling was reported same size.

If more details just tell about.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for providing the test case. For the case where byteenable is moved to avalon_slave, the Platform Designer generates error when the byteenable is set to 2 and Bits per symbol is set to 16, which is correct. The byteenable should be 1 if the Bits per symbol is set to 16 and read/write data width is 16.

When the byteenable is moved to conduit_end, byteenable is set to 2 and Bits per symbol is set to 16, the software did not generate any error message. The byteenable is generated as an input to the conduit_end. No error message is generated because the data transfer proceeds as if all byteenable are asserted if the interface does not have a byteenable signal.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't understand if you say me this is ok or recognize it don't reveal an hardware error.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The software generates an error message when user enters a wrong value for byteenable under Avalon Slave, which alerts user about the wrong setting. I suppose this is the correct behavior where error message is generated for wrong setting.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page