- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

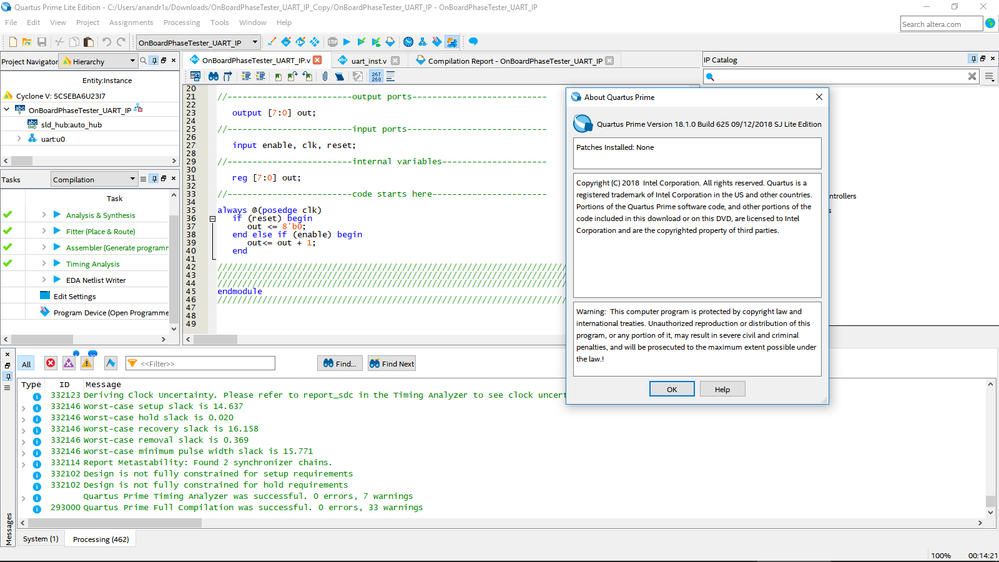

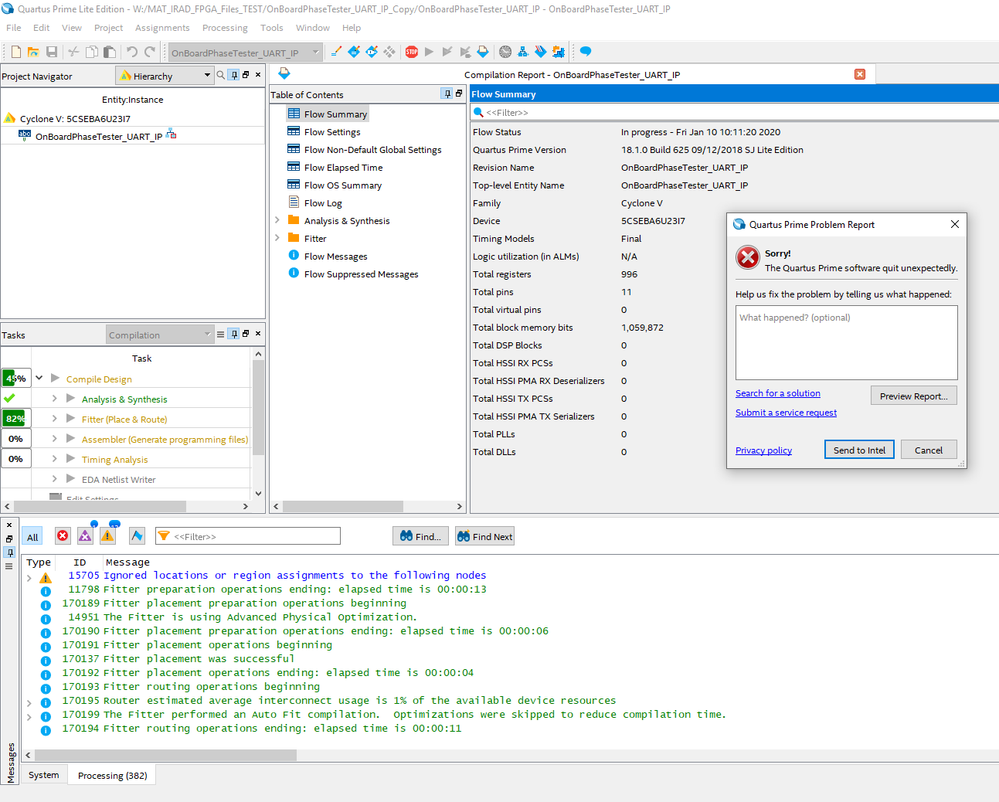

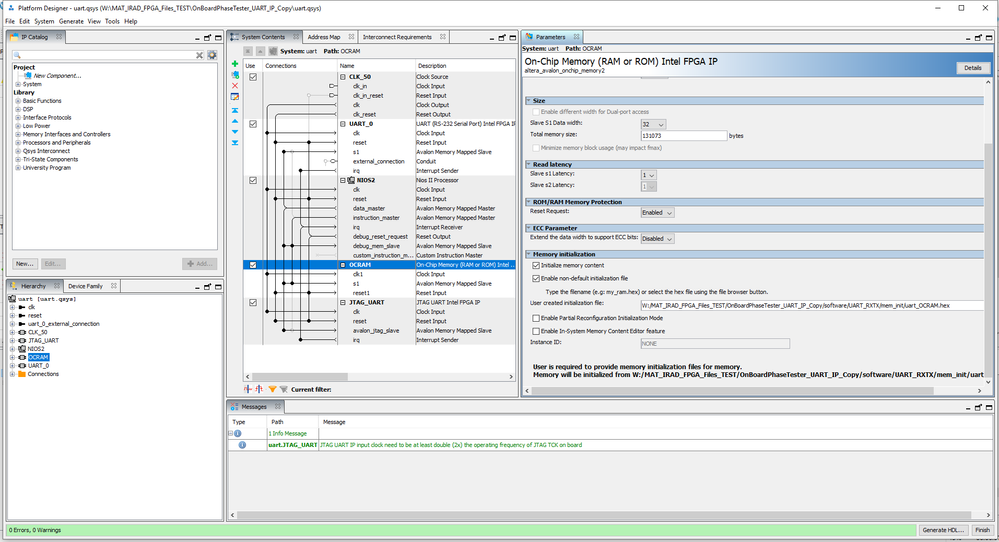

I am trying to integrate UART (RS-232 Serial Port) Intel FPGA IP into my project on a DE10-Nano with a Cyclone V SoC. I have followed the CVSOV UART example from the design store and I have gotten to the point to where I am trying to call the HDL created by the platform designer into my top level code. However, when i try to compile my project I get a popup saying that Quartus Quit Unexpectedly and I do not get an actual error code at all. Furthermore, when I remove the line of code which calls the HDL for the UART generated by the platform designer the code will compile.

Has anyone else seen this kind of error when trying to integrate IP into a design, or am I likely integrating the IP incorrectly? I do not know what this error means.

Thank you in advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I was able to get the project to compile after decreasing the total memory size in the On-chip Memory IP in platform designer. I decreased the memory from about 130000 bytes to 100000 bytes and this seemed to work.

Van

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Van,

Try by deleting incremental_db & db folders.

Also close all the application running.

Regenerate the platform designer system and integrate on top and compile.

Also do share your design.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I had already tried to delete the db folder but I had not tried to delete the incremental _db folder. I did make some changes in the platform designer in the on chip memory IP. The changes were that I changed the name of the IP's in the platform designer to follow the Max Baud Rate Cyclone V SOC Design Example and I changed the On chip memory initialization so that it does not initialize memory content. this allowed the program to compile but It does not allow for the use of the nios ii code I am using.

Here is my design as it stands now:

I altered the code in NIOS to remove some errors in the hex file, regenerated the platform designer, and re-added the platform designer qip fle and qsys file to my project. The on chip memory is still set to initialize my custom nios project and quartus still stops unexpectedly.

I can't post code at the moment because it contains items which are proprietary and I am awaiting approval to post.

Van

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have gotten approval and have modified my original code to replace the proprietary sections with a counter. I still get the same error during the compilation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Not able to replicate the scenario with the project above.

Try by deleting incremental_db & db folders. also check original code.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

With that same project I still get the same error as shown below. To be sure I re downloaded the project from the file I posted above. I have deleted the db and incremental_db and I have tried compiling with no other programs running in the background. The only thing that I have been able to do to stop this error from happening is to comment out line 18 in the top level V file or to go into the platform designer in the on chip memory module under memory initialization and un-check "Enable non-default initialization file" and "Initialize memory content". My assumption is that in order for the UART IP to work I need those two boxes to be checked. Is that assumption correct? Could there be any potential problems in where I have it saved or possibly my compilation settings as well? We are running the same version of quartus.

Van

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Okay, Please click on preview report and attache it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here it is:

Problem Details

Error:

Internal Error: Sub-system: U2B, File: /quartus/db/u2b/u2b_av_m10k_param.cpp, Line: 2085

ram_content_index < ram_content.size()

Stack Trace:

0x10426: U2B_AV_M10K_PARAM_TRANSLATOR::translate_eram_bitvec + 0x5f6 (db_u2b)

0xf2cf: U2B_AV_M10K_PARAM_TRANSLATOR::convert_config_to_physical_atom + 0x12f (db_u2b)

0xcfb4d: U2B_TRANSLATOR_AV_M10K::convert + 0x9d (db_u2b)

0x349d5: FSV_U2B_POSTFIT::check_u2b_configs_for_conflicts + 0x585 (fitter_fsv)

0x396b9: FSV_U2B_POSTFIT::work + 0x139 (fitter_fsv)

0x601ca3: vpr_qi_u2b_postfit_work + 0xc3 (fitter_vpr20kmain)

0x270376: aa_flow_finalize + 0x66 (fitter_vpr20kmain)

0x26b25d: aa_flow_fit + 0x20d (fitter_vpr20kmain)

0x5735ae: VPR_QI_FACADE::vpr_qi_main + 0x6e (fitter_vpr20kmain)

0x3384e: fitapi_run_vpr + 0x7e (fitter_fitapi)

0x1fb8f: FSV_EXPERT_BASE::run_vpr + 0x13f (fitter_fsv)

0x1f64d: FSV_EXPERT_BASE::place_and_route + 0x12d (fitter_fsv)

0x1eab6: FSV_EXPERT_BASE::invoke_fitter + 0x636 (fitter_fsv)

0x1c952: fsv_execute + 0x22 (fitter_fsv)

0xe910: fmain_start + 0x900 (FITTER_FMAIN)

0x41b1: qfit_execute_fit + 0x1bd (comp_qfit_legacy_flow)

0x5384: QFIT_FRAMEWORK::execute + 0x2a0 (comp_qfit_legacy_flow)

0x267f: qfit_legacy_flow_run_legacy_fitter_flow + 0x1c7 (comp_qfit_legacy_flow)

0x14410: TclInvokeStringCommand + 0xf0 (tcl86)

0x161e2: TclNRRunCallbacks + 0x62 (tcl86)

0x17a65: TclEvalEx + 0xa65 (tcl86)

0xa6f8b: Tcl_FSEvalFileEx + 0x22b (tcl86)

0xa5646: Tcl_EvalFile + 0x36 (tcl86)

0x12606: qexe_evaluate_tcl_script + 0x376 (comp_qexe)

0x11864: qexe_do_tcl + 0x334 (comp_qexe)

0x16755: qexe_run_tcl_option + 0x585 (comp_qexe)

0x380c3: qcu_run_tcl_option + 0x1003 (comp_qcu)

0x160aa: qexe_run + 0x39a (comp_qexe)

0x16e51: qexe_standard_main + 0xc1 (comp_qexe)

0x2233: qfit2_main + 0x73 (quartus_fit)

0x12e98: msg_main_thread + 0x18 (CCL_MSG)

0x1467e: msg_thread_wrapper + 0x6e (CCL_MSG)

0x16660: mem_thread_wrapper + 0x70 (ccl_mem)

0x12761: msg_exe_main + 0xa1 (CCL_MSG)

0x287e: __tmainCRTStartup + 0x10e (quartus_fit)

0x17973: BaseThreadInitThunk + 0x13 (KERNEL32)

0x6a270: RtlUserThreadStart + 0x20 (ntdll)

End-trace

Executable: quartus_fit

Comment:

None

System Information

Platform: windows64

OS name: Windows 10

OS version: 10.0

Quartus Prime Information

Address bits: 64

Version: 18.1.0

Build: 625

Edition: Lite EditionVan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Van,

It looks like internal error but however not replicate-able, If possible share complete design.

or

Try using Quartus Lite latest version 19.1.

We can see such error reported on Quarts v13.

https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/solutions/rd07042013_838.html

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I was able to get the project to compile after decreasing the total memory size in the On-chip Memory IP in platform designer. I decreased the memory from about 130000 bytes to 100000 bytes and this seemed to work.

Van

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page