- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi guys,

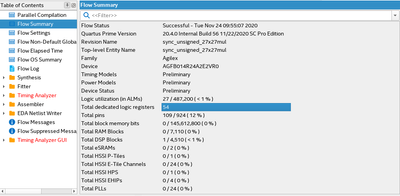

I'm new in Quartus. Had the first verilog code tested as below under Agilex device : AGFB014R24A2E2VR0.

module sync_unsigned_27x27mul (out, clk, a, b);

output [53:0] out;

input clk;

input [26:0] a;

input [26:0] b;

reg [26:0] a_reg;

reg [26:0] b_reg;

reg [53:0] out;

wire [53:0] mult_out;

assign mult_out = a_reg * b_reg;

always@(posedge clk)

begin

a_reg <= a;

b_reg <= b;

out <= mult_out;

end

endmodule

From the compilation report, it said that I had 54x dedicated logic registers fitted into my logic (another 54x into my DSP block). In my design, I should have total of 108x registers. Would like to know what can/should I do to have the fitter places both of my input and output registers into the DSP blocks without using the logic registers?

- Tags:

- dsp

- multiplier

- Verilog

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Beng,

To target the dedicated DSP block architecture in Intel FPGA devices. there are recommended HDL coding styles. you may refer to link below related to Inferring Multipliers and DSP Functions(pg5).

Thanks,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We do not receive any response from you to the previous question/reply/answer that I have provided, thus I will put this case to close pending. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page