- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a question on why does Quartus allow redundant overloaded functions to be compiled without raising an error condition.

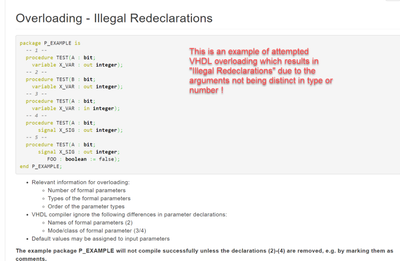

An example overloaded illegal redeclaration in a VHDL package is shown below.

So why does Quartus allow this?

This question is related to my post regarding issues with overloaded functions here:

community.intel.com/t5/Intel-Quartus-Prime-Software/VHDL-Function-Overloading-not-working/m-p/1326778#M71307

Thanks,

James

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi James,

I'm not sure why Quartus doesn't throw an error. May I know which version of Quartus you're using?

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Nurina,

I am using Quartus Prime Standard Edition 20.1.1 Build 720 with Patches Installed 1.08std, 1.02i running on Windows 10 primarily but also on Ubuntu.

Thanks,

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

James, can you provide a small Quartus design which shows that it doesn't throw an error?

Thanks,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Nurina,

I can make a small design and send it to you.

Current design is large and cannot be shared.

Thanks. James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi James, any updates?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I will be posting a small project to github with the example of compiler failure. Thanks. James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi James,

Any updates? If you could upload the design soon we can help you. Otherwise we will be unable to support you.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Will post the example today. Thanks. James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Nurina,

I have posted an example design with the VHDL overloading issue to github here:

https://github.com/saturn77/monitorX

What I did to illustrate the issue:

Nios does the following:

- Writes a value to an output register

- This register is then converted to signed, unsigned, and std_logic_vector type

- The VHDL overloaded "bits" function is then applied to these three signals

- Nios then reads these signals back in along with the original value written

Now what I found was interesting, that the values agree to their types. This is in contrast to my cyclone V design where the values are disagreeing with each other; it seems to be at reset.

However, the fundamental issue remains as to whether Quartus should throw a compiler error to VHDL overloading functions without unique signature, and the project on github does indeed show that Quartus allows these non-unique argument signatures to be compiled.

Thanks,

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Nurina,

I am wondering if you had a chance to run the example design that I posted on GitHub of the overloaded VHDL example. Thanks. James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Nurina,

I am wondering if you had a chance to run the example design that I posted on GitHub of the overloaded VHDL example.

If there is something additional that you would like to see please let me know.

Thanks. James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi James,

Apologies on the late response. I'm getting the below error:

Error (10481): VHDL Use Clause error at pwm_gen_fsm.vhd(4): design library "work" does not contain primary unit "Basic_Data_Types". Verify that the primary unit exists in the library and has been successfully compiled.

I think it's because the file "../source/Basic_Data_Types.vhd" is missing. Can you make sure to include that file in the github?

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Nurina, The basic_data_types.vhd file is included in github now.

The design takes approximately 10 minutes to compile.

Also, if you want to see the uart readout, you need to add a small FTDI usb uart to the gpio pins GPIO_9 (Rx) and GPIO_11 (Tx)

Thanks, James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks James. I am able to replicate the problem you're seeing. I've reported the problem to engineering and will let you know of any updates.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the feedback Nurina. Will look for future updates. James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi James,

I'd just like to let you know that our engineering team is currently investigating the problem. I will let you know if there are any further updates.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Nurina, Thanks for the feedback. I have a large codebase that I inherited with these issues, with this function scattered through out the code base. If there is some sort of fix, it would be most valuable to a current design effort. Also if the engineering team needs anything from me just let me know. Thanks. James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi James,

Just to let you know that our engineering are now focusing feature enhancement/bug fixing on Pro edition. For Standard edition, they will put it as lower priority. We are sorry to inform this.

With that, I shall put this case to a close pending. If you still need further assistance, you are welcome reopen this case within 15 days or open a new case, and someone will help you.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Nurina,

Thanks for the feedback.

Regarding the feedback here, is it true that the engineering team will be addressing the VHDL function overloading issue with the Pro Edition, or a general list of issues/bugs that does not include the overloading issue?

Thanks,

James

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page