- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, reported and disappeared issue was back again:

Quartus Prime Version 18.1.0 Build 625 09/12/2018 SJ Lite Edition

Linux Mint 17.3

Sony vaio SVS1511C5E

Target 10M04SCE144A7G

first issue link:

https://forums.intel.com/s/question/0D50P00004EfVuGSAV/is-if-elsif-else-in-this-case-errant

Compile code where snip is, resulted in wrong synthesis, signal was forever filled with wrong value "00" on two code part: Send REMOTE MAC, Send Remote IP.

Changing if elsif to case on MAC part removed issue to IPAddress too.

Changing from case to if elsif was deterministic :

if elsif elsif : fault .

case: working.

clean project don't affect behavior, so after cleaning same scenario.

Compile on Quartus II version 15.0 resulted in good synthesis on both version.

ANd now nightmare again.... Returning to quartus II version 18.1 upgraded again project cleaned up and wizz of havoc... generated file where ok.....

During debug some more issue appeared somewhere on other working IP core, clean project removed, final version now is working...

Saved all revision but again not able to replicate, I am suspecting some pattern sensitivity to large commented code block and when source file exceed 1K lines.

Difference was commenting if elsif or case as is here, case version .

Actually is build as shown with case commented out.

Test in progress to isolate fault, need full project, cannot replicate on small chunk.

-- aaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaa

-- aaaaaaaaaaaaaaaaaa *** IP MAC SUB state sender ******* aaaaaaaaaaaaaaa

-- aaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaa

-- Send destination MAC address (Remote), return to sm_pktsend_gostate Signal

-- when 11x"08" =>

-- Packet procedure

when pktsend_remotemac =>

if Local_pktgo_nxtstate = '1' then

Local_CRC_RUN <= '1'; -- start crc process

if SendPacketType = IPPKT_ARPReq then

Local_pkt_data<= 8x"ff";

-- else

-- case counter is

elsif counter = 6 then

-- when 6 =>

Local_pkt_data<= RemoteMAC(47 downto 40);

elsif counter = 5 then

-- when 5 =>

Local_pkt_data<= RemoteMAC(39 downto 32);

elsif counter = 4 then

-- when 4 =>

Local_pkt_data<= RemoteMAC(31 downto 24);

elsif counter = 3 then

-- when 3 =>

Local_pkt_data<= RemoteMAC(23 downto 16);

elsif counter = 2 then

-- when 2 =>

Local_pkt_data<= RemoteMAC(15 downto 8);

elsif counter = 1 then

-- when 1 =>

Local_pkt_data<= RemoteMAC(7 downto 0);

-- when others =>

-- end case;

end if;

counter := counter-1;

-- end if;

end if;

if counter = 0 then

-- counter := 6; -- num mac bytes

sm_pktsend_state <= sm_pktsend_gostate; -- pktsend_hostmac; return to caller

end if;

-- Send Source MAC address, return to sm_pktsend_gostate Signal

when pktsend_hostmac =>

if Local_pktgo_nxtstate = '1' then

if counter = 6 then

Local_pkt_data<= HostMAC(47 downto 40);

elsif counter = 5 then

Local_pkt_data<= HostMAC(39 downto 32);

elsif counter = 4 then

Local_pkt_data<= HostMAC(31 downto 24);

elsif counter = 3 then

Local_pkt_data<= HostMAC(23 downto 16);

elsif counter = 2 then

Local_pkt_data<= HostMAC(15 downto 8);

elsif counter = 1 then

Local_pkt_data<= HostMAC(7 downto 0);

end if;

counter := counter-1;

end if;

if counter = 0 then

-- counter := 6; -- num mac bytes

sm_pktsend_state <= sm_pktsend_gostate; -- pktsend_ethernethdr; return to caller

end if;

-- Send HOST IP address, return to sm_pktsend_gostate Signal

when pktsend_hostip =>

if Local_pktgo_nxtstate = '1' then

if counter = 4 then

Local_pkt_data<= HostIP(31 downto 24);

elsif counter = 3 then

Local_pkt_data<= HostIP(23 downto 16);

elsif counter = 2 then

Local_pkt_data<= HostIP(15 downto 8);

elsif counter = 1 then

Local_pkt_data<= HostIP(7 downto 0);

end if;

counter := counter-1;

end if;

if counter = 0 then

sm_pktsend_state <= sm_pktsend_gostate; -- pktsend_ethernethdr; return to caller

end if;

-- Send HOST IP address, return to sm_pktsend_gostate Signal

when pktsend_remoteip =>

if Local_pktgo_nxtstate = '1' then

if counter = 4 then

Local_pkt_data<= RemoteIP(31 downto 24);

elsif counter = 3 then

Local_pkt_data<= RemoteIP(23 downto 16);

elsif counter = 2 then

Local_pkt_data<= RemoteIP(15 downto 8);

elsif counter = 1 then

Local_pkt_data<= RemoteIP(7 downto 0);

end if;

counter := counter-1;

end if;

if counter = 0 then

sm_pktsend_state <= sm_pktsend_gostate; -- pktsend_ethernethdr; return to caller

end if;

end case;

end if; -- clock edge

end if; -- reset

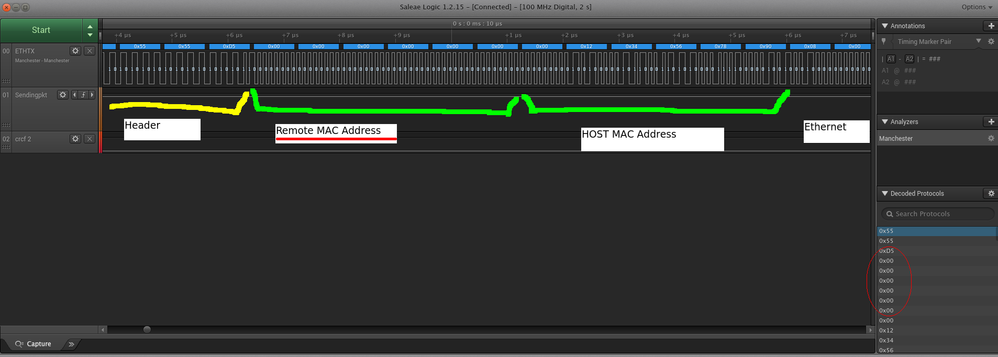

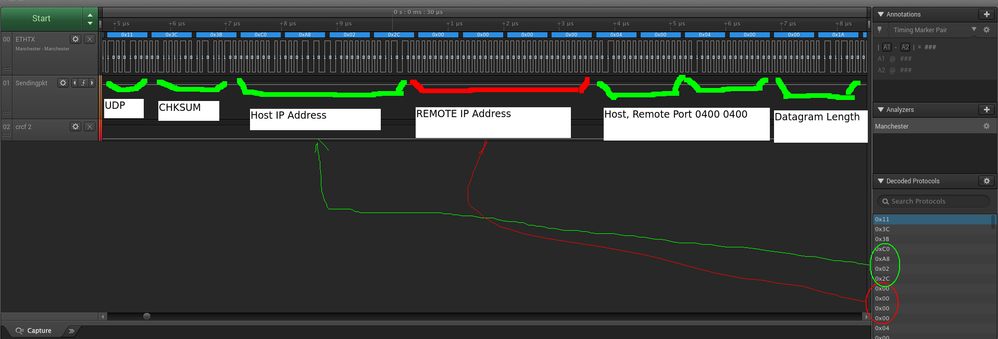

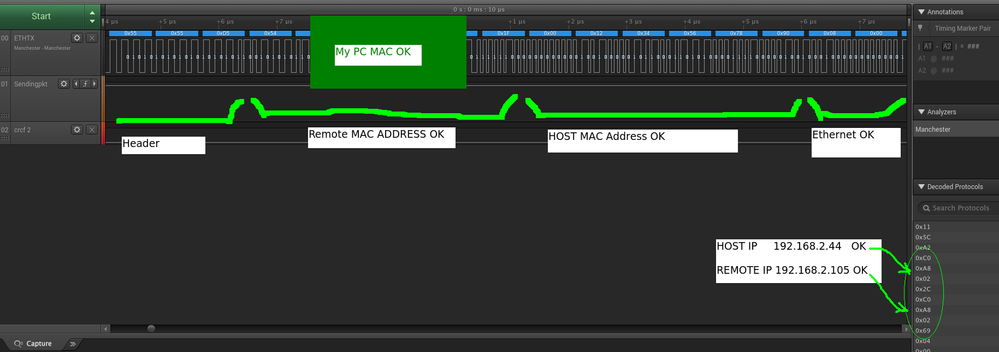

end process;Here saleae LA decoded Ethernet frame:

**** If ELSIF ELSIF

Wrong MAC address set to zero

Wrong IP address set to zero.

**** CASE selector on 18.1 ****

after 15.0 successful build code was reverted as shown on snippet and worked till now never touched.

This issue is driving me crazy debug what has no issue on VHDL but hardware related to wrong coding of tool.

first report on another part of code now rewritten:

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Linux mint is not the official supported OS.

You may use either of the supported OS listed here: https://www.intel.com/content/www/us/en/programmable/support/support-resources/download/os-support.html

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Your answer is useful, same issue on supported platform!

Mint is ubuntu based so sound like supported.

Mint has spread over more than suse and red hat.

I DON'T wish use unity, nor winxx

Quartus Release 15.0 work 18.1 doesn't.

Other issue I reported doesn't work on other Linux nor on winzz.

first column of link report win7 sp1, on that platform fail same way, just 10 time slow than linux or mac.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you provide a test case and steps to reproduce the error?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Edit after post mistype and some missing word:

Actually not, I am exercising a working copy of project VM hosted. Try find a way to reproduce in a stable manner. Issue appear and disappear as from Other user I am interacting to find way to isolate this.

Actual good code was the same one performed bad. More affected target for now seems if elsif construct, leave me some time to test in deep.

On other design/board something similar unaddressed for now but close this issue seems plague LCD controller design too.

More important to me is how to avoid on my production unit.

Actually code classified good (same version issued) passed test stress on hardware. I leave as is for now to finish on time.

Some other board suffer strange similar issue, not understood last test:

LCD controller was good on test platform SC25 based, moved to SC08 LCD Image went fuzzy and out of sync. IP core has a lot of if elsif.

I was never able to reprogram .pof, (issue reported on another post) nor I understood what happened at that time. Left on stand by since November 2018. Also there issue appeared as moving target, never was the same. Last issue just disarmed me thinking of Synthesis failure.

Built just 4 samples prototypes for now, 1 SC25 (with wired LA interface pod was near to working less strange issue on dma rmw registers), 2 SC08, 1 SC04.

Recompiled and reloaded design to competitor device worked as it is.

This board has just MAX 10 on board so it is more difficult inspect, the one I was on has an STM32 processor controlling IP core so it was more simple test.

Now just injected Ethernet controller IP Core with uCless avalon controller deiven fro mUDP datagram. On Monday I start L.A and network inspection of both ram and register in Real Time try pinpoint what fail.

Regards

Roberto

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know if you have any updates? It was mentioned that the behavior is intermittent. Do you see a consistent unexpected behavior in the design?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No, I exported on another design and doesn't work.

Strange behavior, I routed out RXD from Ethernet input LVDS. On LA is just '0'.

On TX appear just ARP replay, This is ok so no idea why it doesn't work.

Rtl simulator doesn't work too.

I am planning trash out everything from Altera, now Intel.

Design work as is on competitor platform, too many error come from tool never addressed.

I try'd constraint as suggested, no difference on constrained or not design.

Issue appear on something is stable for a long time, doesn't change at all where issue is present.

First issue reported:

Signal driving this logic come from received packet on Tx component. From where it is received to when is used some time in the order of uS elapses, signal doesn't change till next received packet, so during alll TX is like a constant.

Second issue:

Signal use a register was set in the previous reception of ARP/ICMP/UDP packet. One byte @10MHz has a period of 800nS, at almost 10 bytes of preamble are 8uS. This way I think is crazy suspect timing closure.

I found too many issue to simulator, programmer, Platform designer...

Found one subtle error on design was not related to this issue.

I cannot waste time to do beta test for free, write a report cost time, I have no time now and delivery date is very close.

Altera now Intel on my view is dead.

Best regards

Roberto

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Roberto,

Just to clarify, is this Intel FPGA Mac IP or hand coded by you ? What tool you were using in the above waveform? Can you use the ModelSim to check the behavior of the above snipped code?

Or

Can you attach the testbench(.vhd) that can run on the above sample code?

Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page