- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sneha_wagh

I am Jingyang and I am assigned to your case.

Are you trying to convert the avalon agent to an axi slave?

You could try connecting an axi bridge to convert them.

Avalon Agent >>> AXI Bridge Master --- AXI Bridge Slave >>> AXI Master Port

The Quartus Platform Designer would connect the Avalon to AXI .

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sneha_wagh

Any update on this case?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jingyang,

Purpose of I2C Slave in our project is as below:

BMC Controller on Board will read the temperature, health status of FPGA via the I2C bus. BMC Controller requests the status via I2C Bus connected to I2C slave. I2C Slave then sends this request to Processor. Processor in turn gathers the relevant information and provides the status back to I2C Slave which in turn passes this information to BMC controller via I2C bus.

The I2C Slave with memory mapped master agent will not solve the purpose.

There is I2C Slave IP comes along with the processor which acts as a processor subsystem IP and it is present in SDM component. If we use the in-built SDM infrastructure of Intel FPGA, we will get our purpose solved. But in our project, we are using our own Processor and not the SDM structure. Thus we need I2C Slave IP component which is exactly same as the one gets enabled when we use in-built SDM architecture.

Thus I think, below infrastructure that you had suggested won't help here:

Avalon Agent >>> AXI Bridge Master --- AXI Bridge Slave >>> AXI Master Port

Also can you comment on mailbox-client IP integrated as a bridge between processor and SDM [SDM: Secure Device Manager is used to access Flash] ?

In case of more understanding, we can have a call.

Regards

Sneha

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sneha

Yeah we could have a call. My timezone is GMT+8, how about yours? Any timeslot that is suitable for you?

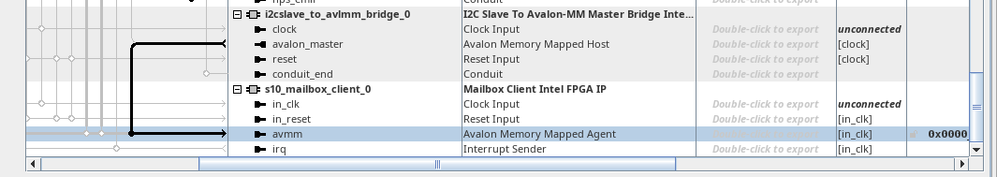

Could the IP you are looking for his the "i2cslave to Avalon-MM Master Bridge"?

It is able to be connected to the "Mailbox Client Intel FPGA IP" and able to export as an i2c slave.

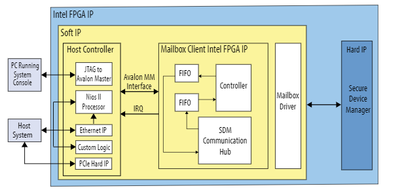

The Mailbox Client Intel FPGA IP is a bridge between a host and the secure device manager (SDM).

In the block diagram below the mailbox is connected to host controller but in your case you could connect it to your processor through the "i2cslave to Avalon-MM Master Bridge"

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sneha_wagh

Is 11am GMT+8 this coming Tuesday a suitable timeslot for you to have a call?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jingyang, can you let me know the corresponding IST timing ?

Regards

Sneha

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jingyang,

Any updates ?

I have one more query. I.e. How to address map the HPS I2C IP in the address range of FPGA Fabric master ?

For example, consider I have JTAG to Avalon Master or any third party processor [Not the ARM processor in HPS system]. Now I need to program registers inside HPS I2C IP master using the above mentioned master. So I would need to know address space of the HPS I2C IP.

Kindly reply as soon as possible, as I am stuck in the middle of project.

Regards

Sneha

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sneha

I have drop you an email on the meeting details.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jingyang,

Timing is suitable and I have joined the meeting.

Regards

Sneha

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Snehar

Great talking to you in the call and better understand what is your problem.

The IP you are looking for should be the " Intel FPGA Avalon® I2C (Host) core"

You could find the details below the link here:

https://www.intel.com/content/www/us/en/docs/programmable/683130/22-1/fpga-i2c-host-core.html

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jingyang,

We won't be able to use the I2C (Host) Core IP as it is the I2C master IP. We are looking for I2C Slave IP. Thus I think, only option remaining is the I2C IP in HPS subsystem that is programmed to behave as slave. I am able to find out HPS IPs registers with the help of following link:

https://www.intel.com/content/www/us/en/programmable/hps/agilex/hps.html

But I was not able to find out programming sequence of I2C Hard IP component.

For our second doubt, i.e. how to address map the bigger region with smaller address width, I am able to find out the address span expander logic.

I have integrated the system and would like to show you the system and would like to take your opinion.

Can we have a call on Monday IST 10 am or any suitable time that overlaps with your and mine time zone ?

Regards

Sneha

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sneha

Yes sure. We can have a call at that time.

We will use back the previous meeting invitation.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sneha

From the connection of i2c slave to Avalon Slave, is not correct.

In the case both end of the connection is not a master, if neither end is a master, the connection would not be reasonable.

In the connection either one end would be a master and the other would be a slave.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, that is the reason, we can not have this I2C with Avalon Memory mapped host IP in our project subsystem.

Thus we thought of using the I2C HPS IP which can be programmed both as master or slave.

I did get the register document of this IP but did not get the programming sequence of the IP. Can you let me know from where I can get this ?

Also I2C HPS IP can work in multi-master mode if programmed as master ?

Regards

Sneha

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Snehal_p

The HPS i2c connection could be a master and also a slave.

The Agilex HPS is a Hard Processor System which contains a quad A53 MPCore Processor.

To use the HPS, you would require to create a baremetal program or a linux operating system and application to interface with the i2c and Avalon Memory.

The i2c connection created in the Quartus will show up in the Linux environment as an i2c device.

You could refer to the link below on the Golden Software Reference Design for the HPS.

https://www.rocketboards.org/foswiki/Documentation/AgilexSoCGSRD

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Jingyang.

Now I think, I2C related queries are resolved. I also got the document for HPS peripherals at the intel site. Able to integrate the HPS subsystem.

I will need some help to clear my understanding related to mailbox client. Keeping this post open till that time.

Regards

Sneha

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sneha

Any update on the case?

Do you still need any more support for the SDM IP?

Regards

JIngyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jingyang,

I would like to understand, if we want to test the QSPI access via Mailbox client IP in simulation environment then what could be the procedure ?

Also want you to show you the mailbox client subsystem connectivity and the configuration pins needed for the FLASH connection.

Can we have a call on Monday at IST 10 am ?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sneha

Could these document be the information that you wanted on the mail box?

Here is an example program of the mailbox.

Related to the signal description you could find them listed here in section 1.2:

Regarding simulation you could follow the steps here to generate the simulation for the mailbox IP.

https://www.intel.com/content/www/us/en/docs/programmable/683102/21-3/simulating-cores.html

If not could we have a call tomorrow instead at 10am IST?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jingyang,

Thanks for the information.

After going through the documents, understood the details of design. Now as of now, I have one query:

1. Lets assume that we are trying to make access to QSPI Flash with the help of Mailbox Client IP. Here, how we can test the transactions sent to mailbox client are getting converted to QSPI commands ?

I.e. If we make some Avalon transactions to avmm port of the mailbox client related to QSPI access , they will eventually will transferred to QSPI pins. How to access the QSPI pins in simulation ? As the pins are not available inside DUT to view to user.

To understand this, I would recommend a call.

Regards

Sneha

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page