- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Try'd add a small rom or initialized ram block on max10 project, resulted ni an error when building assembler file:

Error (14703): Invalid internal configuration mode for design with memory initialization

Error: Quartus Prime Assembler was unsuccessful. 1 error, 1 warning

Error: Peak virtual memory: 824 megabytes

Error: Processing ended: Thu May 2 14:05:19 2019

Error: Elapsed time: 00:00:01

Error: Total CPU time (on all processors): 00:00:01

Error (293001): Quartus Prime Full Compilation was unsuccessful. 3 errors, 156 warnings

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Error is related to Invalid internal configuration mode

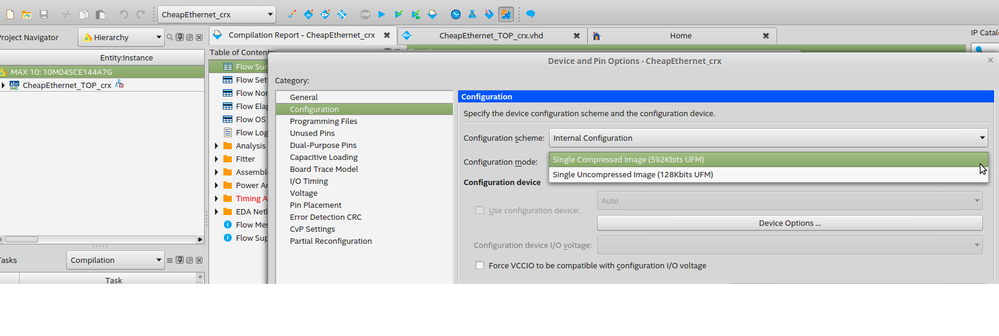

- Is tools configuration mode set to Single uncompressed image with Memory Initialization or Single compressed image with Memory Initialization?(Assignments->devices->device&pins->configuration->configuration mode)

- Is reset and exception vector memory pointing to On-chip RAM?

Refer below link

https://www.youtube.com/watch?v=0k4AZmdW9Sk

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Best Regards,

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anand, Video refer to a NIOS application, I seen it use an SA device, I am using an SC04.

On this family is still present UFM but no initialized memory settings, just compressed uncompressed:

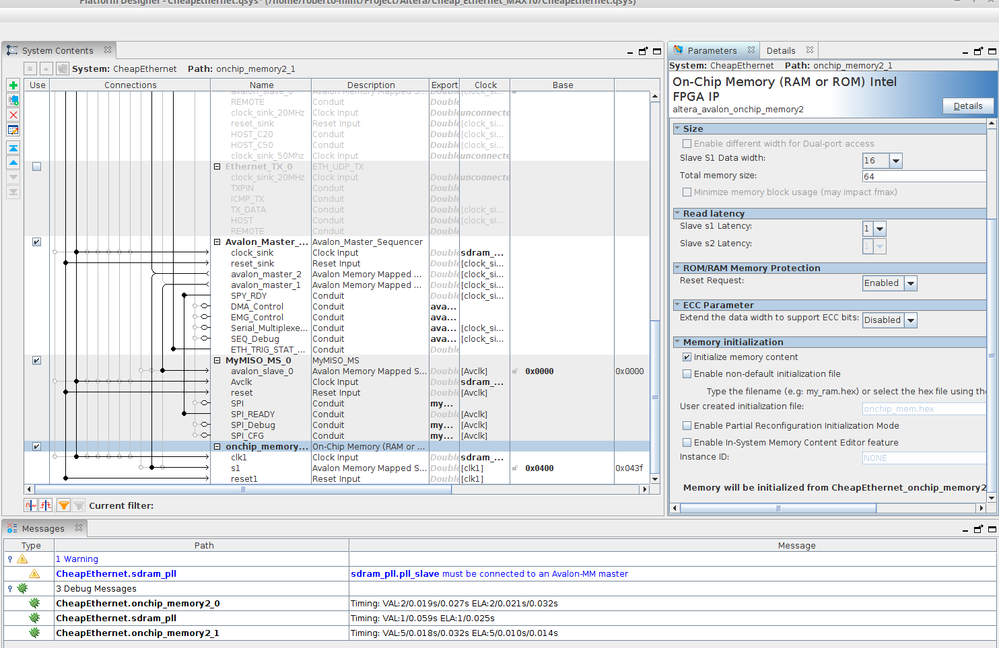

Project has no NIOS, I just need a small ROM or simply initialize ram when no processor on board.

As test, Rom where attached to Master sequencer. Master sequencer is controlled by An STM32 so here is simple to initialize ram or rom by DMA access or fire UDP send request a packet to load memory.

On design where fixed sequence are in place a small rom can reduce a lot LE usage.

I ask again JohnT about limit of SC family, I fear SC cannot support NIOS too.

Regards

Roberto

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Roberto,

Yes, We can use RAM IP and simply initialize ram when no processor on board.

With Is tools configuration mode set to Single uncompressed image or Single compressed image.

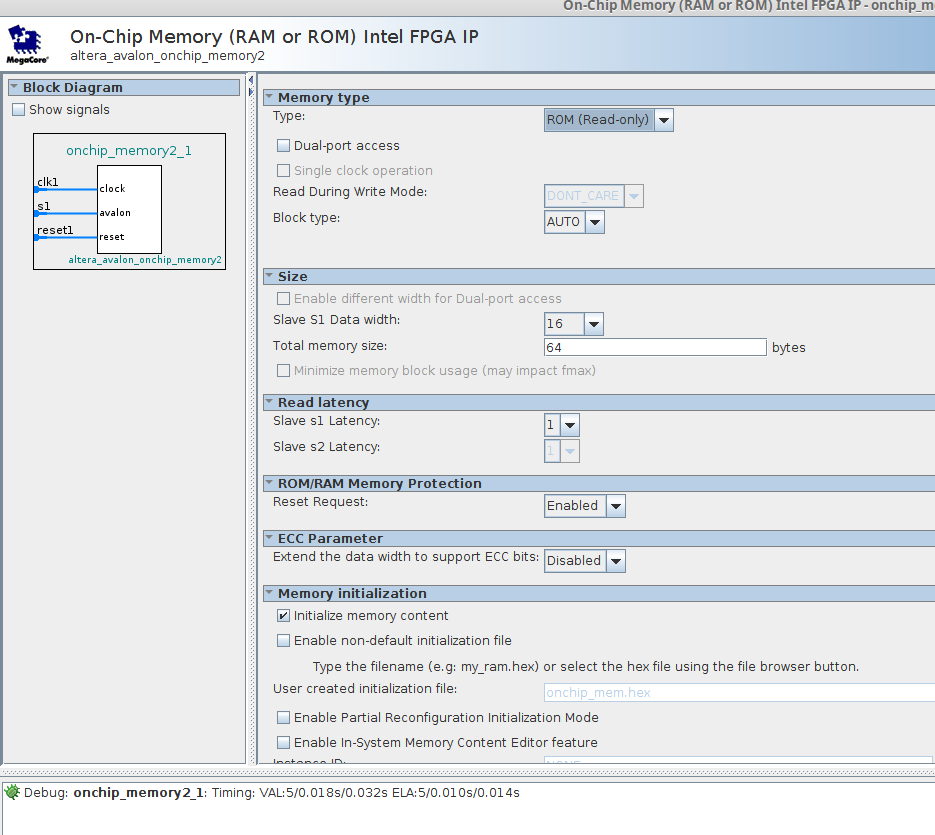

I have checked it using simple ram IP with memory size of 32 bytes of 8 bits data width & memory initialization as shown in image.

Can you share your design?

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

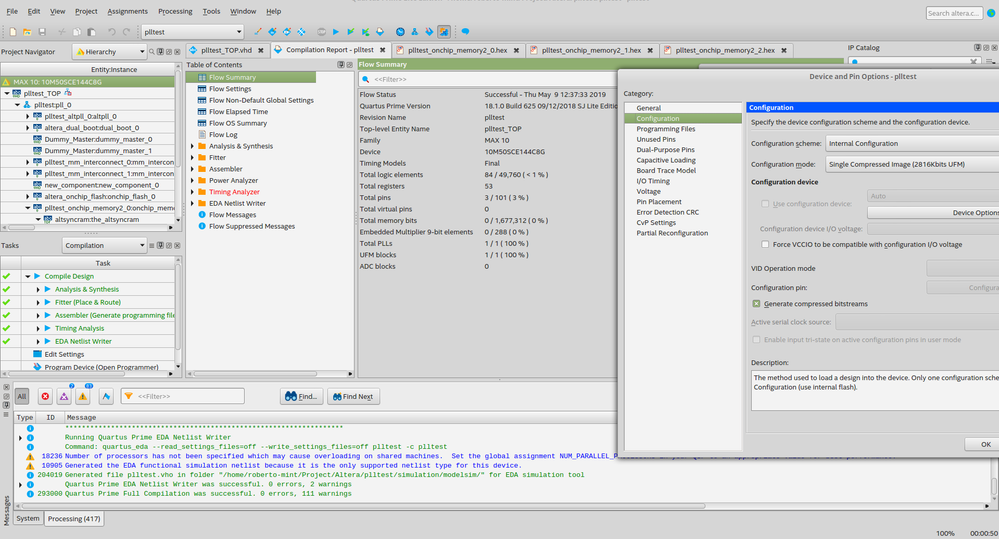

Anand, I have to say You are right on this, I try'd a simple bench and I am able too init ram and rom, I inferred you are on Win platform, I seen a C:\ hardwired orror and long time to produce assemble file than few second...

Here simple (Succesful design) and screenshot, I now revert to large design and see if can use there a small IP parameter rom core.

Test on rom, ram single port, dual port too, so no question on basic IP Core, I fear about another interaction to plague large design as If Then Elsif fail.

Intermixed single dual port ram with different port size, imported core where intend to be attached on large project doesn't fail.

No issue here, this is another point to add to sensitivity list on the failing designs... Set again init ram to Ethernet project same issue I reported here. No idea how to fire this on simple design same as If then elsif.

Imported Ethernet, Avalon DMA Sequencer, STM32 SPI interface, no way to reproduce issue, I take some time to inspect design, I cannot share, so I am in touch with Ktan9.

I am busy now, this evening I try a fresh project just importing files and Qsys.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @RRomano001 for update.

Please do share the solution after debugging your design.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Anand,

it almost like being in a battle zone!

It's almost like being in quicksand.

...

Milestone posed till now:

- Small project seems didn't suffer from this issue nor from other appear from land of Havoc.

- Code on release perform different way when something touched on.

- Perform like memory leakage on synthesis (or assembler) tool when large core have to be fit together.

- (Murphy law) You add some piece to observe bug and it hide from you till remove.

- After toll removed something else broke out

- Memory error is persistent on final code and forever memory init is added to assembler fail.

Whats the bug today?

your link from Email:

AnandRS, I feel proud is some solution can be found on my design but what I feel is fear about Quartus unreliability.

This resemble similar experience on competitor code when they moved from unix platform to M$ tools. Forever appeared "memory assert failure" and never core compiled as it where written, input was set as output, seen from low level files..

This was 20 year ago, competitor learn lesson, I fear Altera got it LARGE quicksand experience.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page