- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

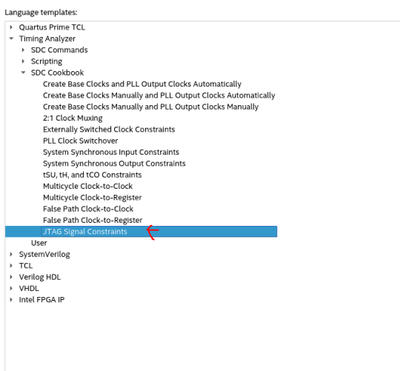

The path below failed the setup timing. The sdc are from the template.

How to fix this setup violation? I am using Quartus Pro 22.3

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Chris,

In the jtag constraint look for

proc set_tck_timing_spec { } {

# USB Blaster 1 uses 6 MHz clock = 166.666 ns period

set ub1_t_period 166.666

# USB Blaster 2 uses 24 MHz clock = 41.666 ns period

set ub2_default_t_period 41.666

# USB Blaster 2 running at 16 MHz clock safe mode = 62.5 ns period

set ub2_safe_t_period 62.5

In snipper above,you may comment 16MHz and 24Mhz, and

set tck_t_period $ub2_default_t_period

change the $ub2_default_t_period --> ub1_t_period

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Chris,

May I know what frequency you are running for TCK? 24MHz? You need to lower the tck clock rate of UBII. "Lower the tck clock rate of UBII." refers to change in the UBII hw. Then, update .sdc accordingly to confirm with STA. There are a few valid values. 24MHz, the default on UBII, is very hard to meet. 16MHz is more usable without really noticeable performance difference.

The value change is not persistent. Need to reapply upon power cycle of UBII. The lowest UBII supported tck is 6MHz. In this case, you can set to 6Mhz and perhaps the violation is gone.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am just inserting the Jtag sdc from the template. Do I need to specially constrain the clock signal? Could you share the sdc that I need to add into the file?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Chris,

In the jtag constraint look for

proc set_tck_timing_spec { } {

# USB Blaster 1 uses 6 MHz clock = 166.666 ns period

set ub1_t_period 166.666

# USB Blaster 2 uses 24 MHz clock = 41.666 ns period

set ub2_default_t_period 41.666

# USB Blaster 2 running at 16 MHz clock safe mode = 62.5 ns period

set ub2_safe_t_period 62.5

In snipper above,you may comment 16MHz and 24Mhz, and

set tck_t_period $ub2_default_t_period

change the $ub2_default_t_period --> ub1_t_period

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

May I know if there is any update from previous reply?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am still trying, I will update when I have the result

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The suggestion works. Thank you SyafieqS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution, give Kudos and rate 10/10 survey

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page