- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I used the State Machine Wizard to create a machine with 9 states. Looking through the generated code I saw this:

reg [8:0] fstate;

reg [8:0] reg_fstate;

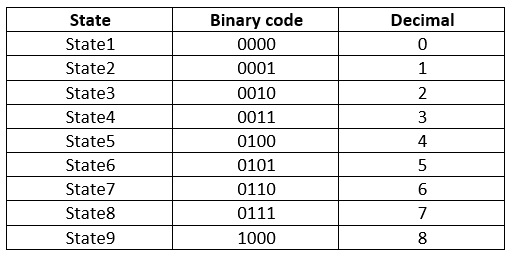

parameter State1=0,State2=1,State3=2,State4=3,State5=4,State6=5,State7=6,State8=7,State9=8;The registers are 9 bits whereas the states only require 4 bits because they are binary encoded:

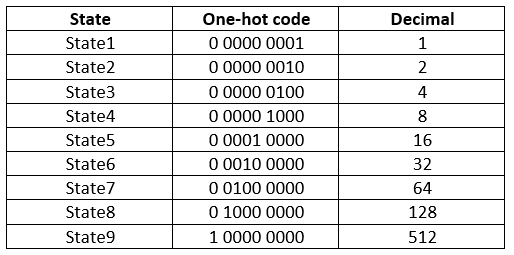

It seems as if the registers are expecting one-hot encoding (9 bits for 9 states):

The state machine seems to work correctly using binary encoding, but the registers have several unused/wasted bits.

Is this a bug?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Tim10,

If implemented in fpga fabric, it is much more efficient to use the bit-by-bit approach compared to a counter approach.

So the total amount of space used is less. An FPGA does not have an ALU as a microprocessor does have.

Best regards,

Johi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johi,

That's a good point, but the wizard has generated 9-bit registers for one-hot encoding, yet generated state parameters using binary encoding, which is inconsistent.

From reading Efficient State Machine Design it seems that the actual encoding and therefore the size of the registers are determined at a later stage in the design flow, so the wizard's inconsistency at the initial Verilog stage seems irrelevant.

Thanks,

Tim.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The "StateX=N" is using N as the bit number. Quartus will by default decompose state machines and reencode them as one-hot, as this form is much more resource efficient when implementing in the FPGA. You can direct Quartus not to do this by adding the syn_encoding attribute to the Verilog source on the state machine definition. Or to influence all state machines, in the .qsf file use the state_machine_processing directive as in:

https://www.intel.com/content/www/us/en/programmable/quartushelp/current/index.htm#logicops/logicops/def_smp_process_type.htm

The default is 'auto', where Quartus will decide the 'best' encoding that meets timing and uses minimal resources. Choose 'user-encoded' if you want quartus to leave as is.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page