- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm trying to support the synthesis of my system on both Vivado and Quartus. So far i've had tough luck with Quartus (probably due to my inexperience).

I have a package in which i have some functions which set up my local parameters in other RTL files. The functions look like:

function automatic int get_settings_loading_serialised_width( );

int settings_loading_serialised_width = `REG_STATUS_FLAG_WIDTH +

`REG_K_WIDTH +

`L_C_WIDTH +

`L_A_WIDTH +

get_u_width() +

`REG_ID_WIDTH +

`L_E_REG_QM_WIDTH +

15 +

`REG_N_WIDTH +

$clog2(41+1) +

$clog2(211) +

`REG_NU_WIDTH;

return settings_loading_serialised_width;

endfunctionThere are some additions from the macros included within the package (eg: `REG_N_WIDTH )and some additions from the functions within the package (eg: get_u_width()). I then import this package within my top level module as localparam GET_SETTINGS: get_settings_loading_serialised_width( ) but i get the error: Verilog HDL Defparam Statement error at <location>:. Vivado does not have a problem with this.

P.S. I found that doing something like int a; a = `something; return a; works fine as compared to when int a = `something; return a;

Can anyone please help me with this?

Regards.

- Tags:

- 1 Quartus

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know the software edition(Standard/Pro) and version you are using. Could you provide the .qar file for investigation?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using Quartus Prime 18.1 (standard). I've found the problem. Apparently for Quartus, having a declaration and initialization on the same line (e.g int a = 10 -> Quartus treats this as a non-constant expression) is different from having a separate line for variable declaration and initalization (int a; a = 10; ->Quartus apparently likes this). This is very bizarre. I don't fully understand why this is the case.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

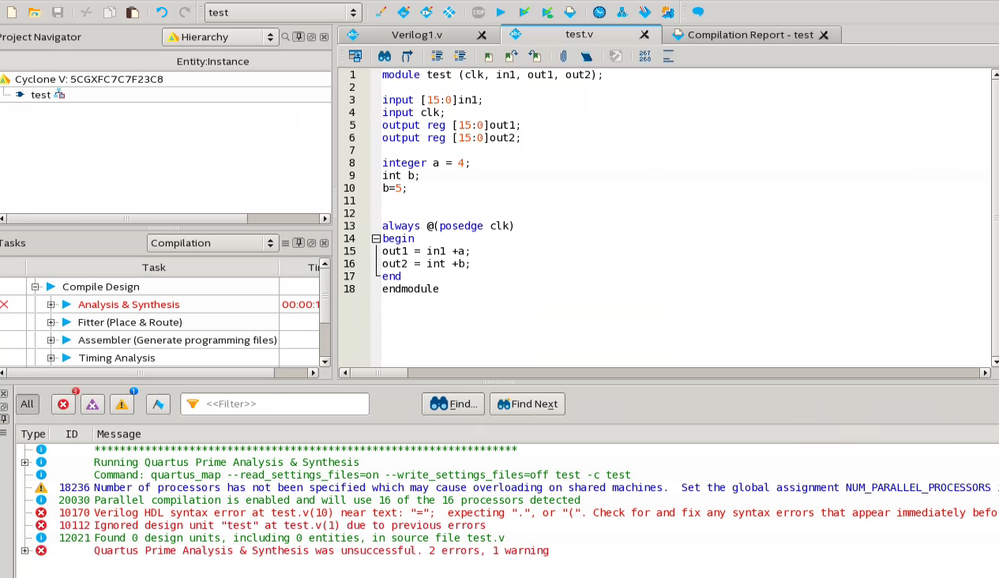

I cannot reproduce the error in your previous reply. Using int in the verilog file caused a syntax error. Could you provide the qar file for investigation?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It's against my company policy to do so. Apologies for that.

If you really want to recreate it. Try doing what i did in the question i asked above. That function is inside a package and is imported within a module. Try compiling it in Quartus that way.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I try to use int in the verilog HDL and the software issues a syntax error message. Could you provide a simple test case that can reproduce the error?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you have any updates?

Thanks.

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page