- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is a new thread that continues another one found here (https://forums.intel.com/s/question/0D70P000006w2HT/tcl-error-error-argument-nodeobject-is-an-object-filter-that-matches-no-objects-specify-one-matches-only-one-object-when-using-lvds-serdes-ip?s1oid=00DU0000000YT3c&s1nid=0DB0P000000U1Hq&emkind=chatterCommentNotification&s1uid=0050P0000082as6&emtm=1587458498799&fromEmail=1&s1ext=0)

Issue: using LVDS SERDES IP core, the full compilation stops in the Timing Analysis phase, with the following error: "Tcl error: ERROR: Argument <node_object> is an object filter that matches no objects. Specify one matches only one object"

This happens in:

- Quartus Pro 19.3

- Quartus Pro 19.4

- Quartus Pro 20.1

The same design in Quartus Pro 19.1 works flawlessly.

As specified, the .sdc file contains the -create_base_clocks option

Attachment: a reduced version of the full project that has however the issue.

Regards and thanks in advance.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

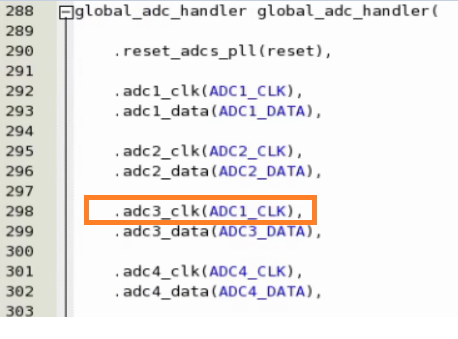

Upon checking, this is caused by the typo in Arria10_DAQ.v (Line 298)

After replacing line 298 with .adc3_clk(ADC3_CLK), you will see Fitter error below:

Error(14566): The Fitter cannot place 1 periphery component(s) due to conflicts with existing constraints (1 IOPLL(s)). Fix the errors described in the submessages, and then rerun the Fitter. The Intel FPGA Knowledge Database may also contain articles with information on how to resolve this periphery placement failure. Review the errors and then visit the Knowledge Database at https://www.altera.com/support/support-resources/knowledge-base/search.html and search for this specific error message number.

Error(175001): The Fitter cannot place 1 IOPLL, which is within LVDS SERDES Intel FPGA IP adc_lvds_rx_altera_lvds_1940_p47vjlq.

Info(14596): Information about the failing component(s):

Info(175028): The IOPLL name(s): global_adc_handler|adc_lvds_rx3|lvds_0|core|arch_inst|internal_pll.pll_inst|altera_lvds_core20_iopll

Error(16234): No legal location could be found out of 16 considered location(s). Reasons why each location could not be used are summarized below:

Error(175006): There is no routing connectivity between source pin and the IOPLL

Info(175026): Source: pin ADC3_CLK

Info(175015): The I/O pad ADC3_CLK is constrained to the location PIN_AL5 due to: User Location Constraints (PIN_AL5)

Info(14709): The constrained I/O pad is contained within this pin

Info(175021): The pin was placed in location pin containing PIN_AL5

Error(175022): The IOPLL could not be placed in any location to satisfy its connectivity requirements

Info(175029): 14 locations affected

Info(175029): IOPLL_2A

Info(175029): IOPLL_2F

Info(175029): IOPLL_2G

Info(175029): IOPLL_2H

Info(175029): IOPLL_2I

Info(175029): IOPLL_2J

Info(175029): IOPLL_2K

Info(175029): IOPLL_2L

Info(175029): IOPLL_3C

Info(175029): IOPLL_3D

Info(175029): IOPLL_3E

Info(175029): IOPLL_3F

Info(175029): and 2 more locations not displayed

Error(20196): Location(s) already occupied and the components cannot be merged. (2 locations affected)

Info(175029): IOPLL_3A. Already placed at this location: IOPLL global_adc_handler|adc_lvds_rx1|lvds_0|core|arch_inst|internal_pll.pll_inst|altera_lvds_core20_iopll

Info(175029): IOPLL_3B. Already placed at this location: IOPLL global_adc_handler|adc_lvds_rx2|lvds_0|core|arch_inst|internal_pll.pll_inst|altera_lvds_core20_iopll

This error indicates that there is another design component already placed at this location and the two components are not mergeable. Refer to details in Info(175029)

To fix this fitter error, reassign ADC3_CLK to other pin location. After reassigning the pin location, the compilation passed without the error

Error(23035): Tcl error: ERROR: Argument <node_object> is an object filter that matches no objects. Specify one matches only one object.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is not a typo, it is intentional.

I'm driving two LVDS SERDES RX IP cores with the same clock because I do not have space for other pins (and as you said only 1 PLL for every bank), so two ADCs are read with the same clock.

Quartus 19.1 correctly understands this and generates two instances of LVDS IP connected to the same clock that shares the same PLL.

Do you suggest that I have to try and merge the two LVDS cores that have the same clocks, i.e. from 2 LVDS of 8 bits to 1 LVDS of 16 bits, for example?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I just notice that the error is different from the error in previous forum thread. Please allow me some time to investigate the issue.

Error(23035): Tcl error: ERROR: Argument <node_object> is an object filter that matches no objects. Specify one matches only one object.

while executing

"get_node_info -clock_edges $fclk_name"

invoked from within

"if {$::RSKM_USE_MICRO == 1} {

if {$is_gui == 1} {

set setup_rpt [report_timing -setup -through $lvdsin_name -to [get_keepers $reg..."

invoked from within

"foreach_in_collection i_non_dpa_keeper $non_dpa_keepers_collection {

set keeper_name [altera_iosubsystem_get_timequest_name [get_node_info -name..."

(procedure "altera_iosubsystem_report_rskm" line 35)

invoked from within

"altera_iosubsystem_report_rskm"

invoked from within

"report_rskm -panel_name "Report RSKM" -stdout -quiet"

(procedure "generate_compiler_post_reports" line 78)

invoked from within

"generate_compiler_post_reports"

(procedure "generate_default_reports" line 193)

invoked from within

"generate_default_reports options"

invoked from within

"if [is_project_open] {

# The all_corners option can be set by INI as well.

set all_corners_ini [get_ini_var -name "qsta_all_corners"]

if {[stri..."

(procedure "main" line 129)

invoked from within

"main"

(file "<Quartus installation directory>/common/tcl/internal/qsta_default_script.tcl" line 1613)

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Kindly change the below:

In the file:

verilog_code/adc/adc_lvds_rx/altera_lvds_core20_191/synth/sdc_util.tcl

Change this line:

set fclk_name "${lvds_instance_name}${RX_NON_DPA_FCLK_TRAIL}"

To this line:

foreach_in_collection lvds_node [get_nodes -nowarn "$lvds_instance_name|*|fclk"] { set fclk_name [get_node_info -name [get_edge_info -src [get_node_info -clock_edges [lindex $lvds_node 0]]]]; break }

Note that if the IP is regenerated, you have to update this line in the SDC again.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY,

thanks for the fix! Changing the line solves the problem.

I've tried it in Quartus Pro 20.1, with and without IP regeneration and works!

I have to keep this fix until the next revision of Quartus, I suppose.

Regards,

Gabriele

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Gabriele,

Yes. You have to apply the same changes when you see the error in the software.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

the solution worked for me in Quartus 19.3 as well. See more info https://forums.intel.com/s/question/0D70P000006iNdK/tcl-error-error-argument-nodeobject-is-an-object-filter-that-matches-no-objects-specify-one-matches-only-one-object-when-using-lvds-serdes-ip

I also used a similar solution in the "altera_lvds_core20_191\synth\lvds_rx_altera_lvds_core20_191_5u346cy.sdc" file to get rid of some warning messages.

I replaced

set pll_fclk_tree_name "${lvds_clock_tree_inst_name}|lvdsfclk_in"

with

foreach_in_collection lvds_node [get_nodes -nowarn "$lvds_instance_name|*|fclk"] { set pll_fclk_tree_name [get_node_info -name [get_edge_info -src [get_node_info -clock_edges [lindex $lvds_node 0]]]]; break }

and

set pll_lden_tree_name "${lvds_clock_tree_inst_name}|loaden_in"

with

foreach_in_collection lvds_node [get_nodes -nowarn "$lvds_instance_name|*|loaden"] { set pll_lden_tree_name [get_node_info -name [get_edge_info -src [get_node_info -clock_edges [lindex $lvds_node 0]]]]; break }

Regards

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael,

It is glad that the solution in the post solves the error in your design. Thanks for the update. This is beneficial to other customer who faces the same problem.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have written a script that allows for a more or less automatic solution within Quartus to replace the line causing the error. As it is possible to execute a tcl script after quartus_ipgenerate to replace the line in sdc_util.tcl, I wrote such a script.

The content of the script is:

set module [lindex $quartus(args) 0]

if [string match "quartus_ipgenerate" $module] {

post_message "Correcting name of LVDS clock tree instance"

set timestamp [clock format [clock seconds] -format {%Y%m%d%H%M%S}]

set filename "ip/../xxx_lvds_rx/altera_lvds_core20_191/synth/sdc_util.tcl"

set temp $filename.new.$timestamp

set backup $filename.bak.$timestamp

set in [open $filename r]

set out [open $temp w]

# line-by-line, read the original file

while {[gets $in line] != -1} {

if {[string first "set fclk_name" $line] != -1} {

set line " foreach_in_collection lvds_node \[get_nodes -nowarn \"\$lvds_instance_name|*|fclk\"\] { set fclk_name \[get_node_info -name \[get_edge_info -src \[get_node_info -clock_edges \[lindex \$lvds_node 0\]\]\]\]; break }"

}

# then write the transformed line

puts $out $line

}

close $in

close $out

# move the new data to the proper filename

file link -hard $backup $filename

file rename -force $temp $filename

}You have to set the filename to the correct location.

Additionally, add the following line to .qsf file:

set_global_assignment -name POST_MODULE_SCRIPT_FILE "quartus_sh:name_of_script.tcl"

Maybe, this solution is benificial for someone, therefore I decided to share it with you.

-Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael,

Thanks for sharing to other users :)

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page