- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

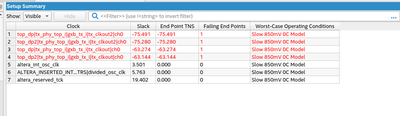

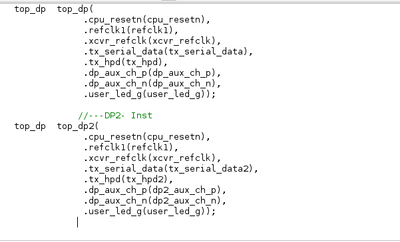

I have generated an example design for display port which compiled successfully. As we are dealing with 2 display ports i made a second instantiation of the same example top. this time i got a timing violation in the following path, which I could not solve. But the project is working fine when I test in the board. Can you please help me to solve this timing violation?

Here is the details of timing violation

ex:

Critical Warning: Unexpected timed setup path

From: top_dp|tx_phy_top_i|gxb_tx_i|gxb_tx|g_xcvr_native_insts[0].ct2_xcvr_native_inst|inst_ct2_xcvr_channel_multi|gen_rev.ct2_xcvr_channel_inst|gen_ct1_hssi_pldadapt_tx.inst_ct1_hssi_pldadapt_tx|pld_pcs_tx_clk_out2_dcm

To: top_dp2|tx_phy_top_i|gxb_tx_i|gxb_tx|g_xcvr_native_insts[0].ct2_xcvr_native_inst|inst_ct2_xcvr_channel_multi|gen_rev.ct2_xcvr_channel_inst|gen_ct1_hssi_pldadapt_tx.inst_ct1_hssi_pldadapt_tx~pld_tx_clk2_dcm.reg

Source Clock: top_dp|tx_phy_top_i|gxb_tx_i|tx_clkout2|ch0

Destination Clock: top_dp2|tx_phy_top_i|gxb_tx_i|tx_clkout2|ch0

component instantiation.

refclk1 is 100MHz

xcvr_refclk is 135Mhz

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for using Intel Communities. Can you share your design?

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you. You are using Quartus 22.2?

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you. I think I found the issue, but first can you share the original example design for only one display port?

Thanks,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

At first I thought there was something wrong with the SDC constraints. But looking into the original example design I suspect there's a misconnection somewhere in your design so I'm reassigning your case to XCVR expert.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Paul,

Apologize for the delayed response as there is some technical difficulty.

I have reviewed the design you shared here.

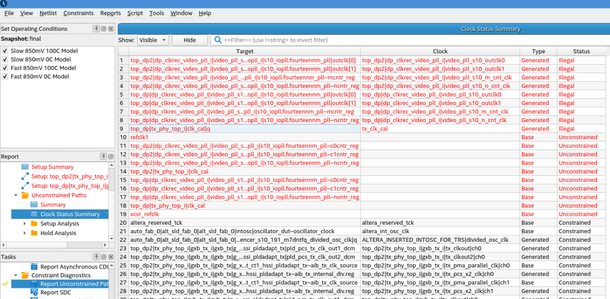

After further discussion, I found that there are a lot of clocks unconstrained and require to add sdc for these clocks.

Our internal team has modified the dp.sdc file and the timing result looks ok.

You may copy the dp.sdc file attached here and replace in your "\\designfile\fpga_top_intg_22_2_0_94(1)_restored\golden\golden_reset_sync_folder_structured\mySDC" directory, then re-compile the design.

Hope this answers your question.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Paul,

Good day.

We do not receive any response from you to the previous answer that I have provided.

With that said, this thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page