- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

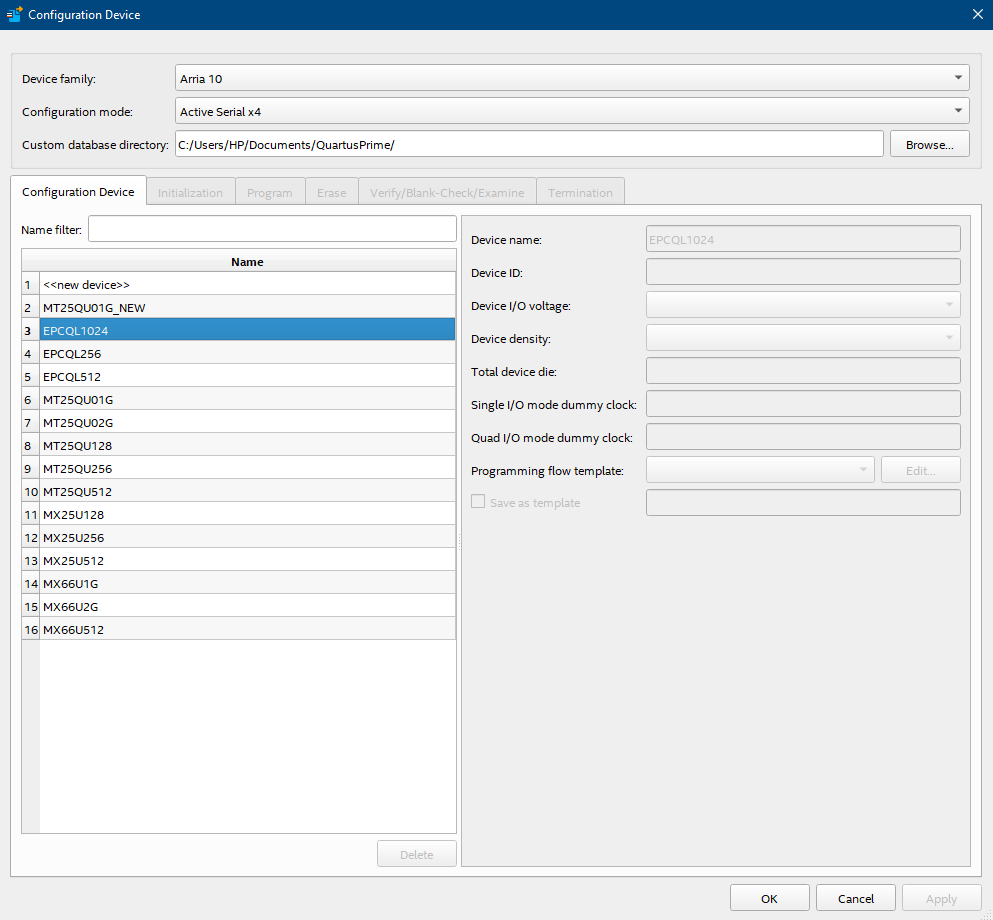

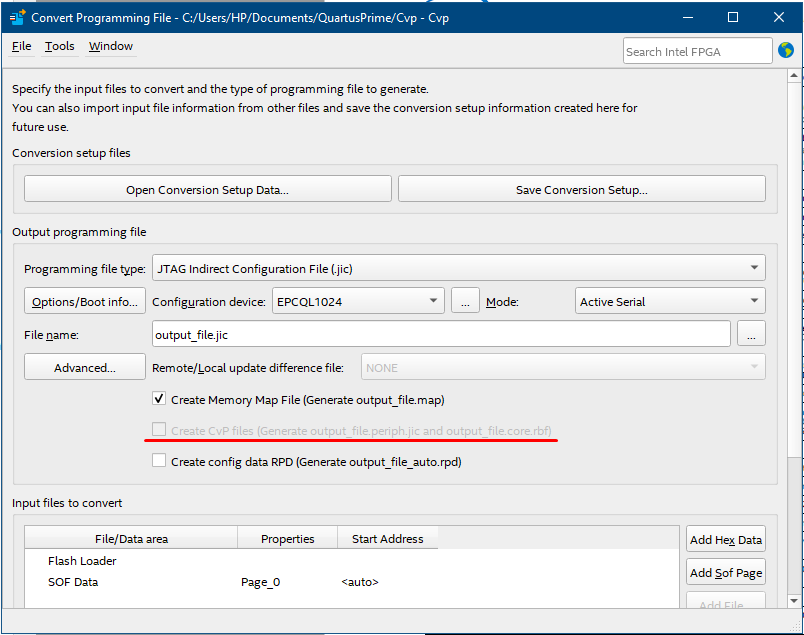

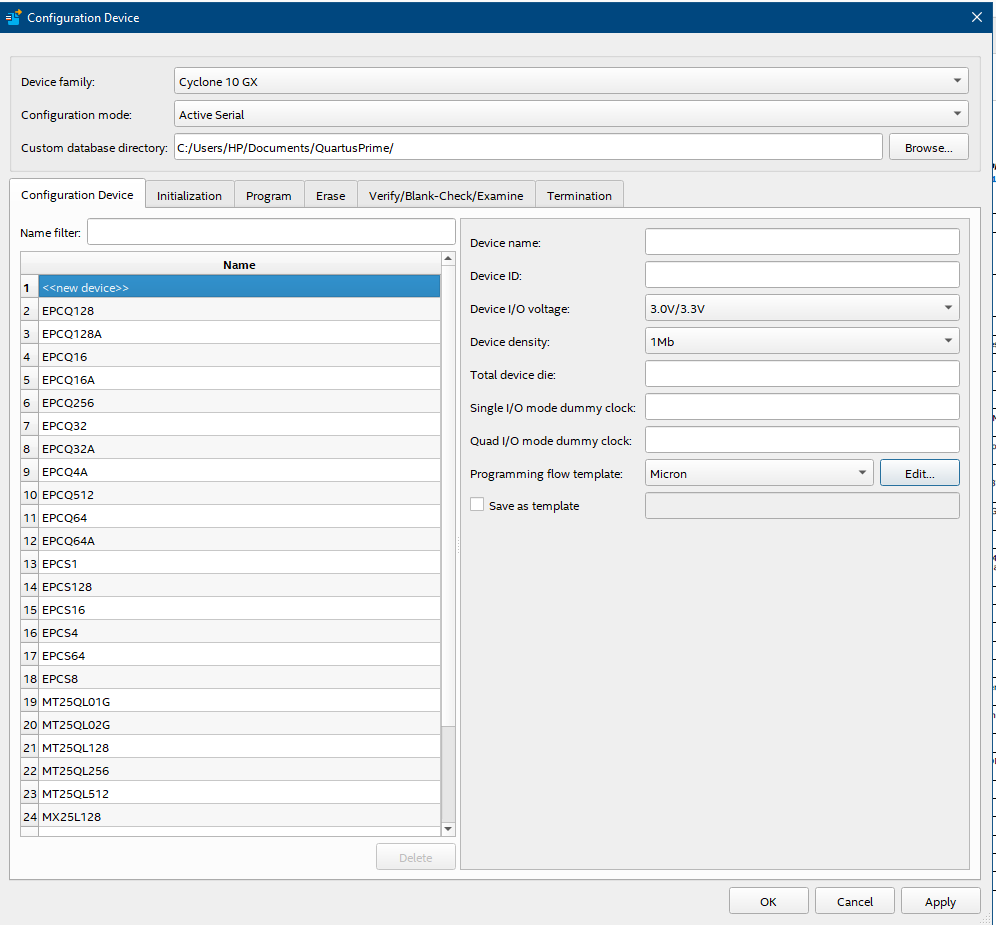

I'm using the Intel® Cyclone® 10 GX CvP Initialization over PCI Express User, so i'm set the ProgrammingFile Type as JTAG Indirect Configuration File (.jic), but when i choose the configuration device as Cyclone 10 family is not found the EPCQL1024. But when i change the family device to Arria the EPCQL is availabel. Why does this happen?

But even with the EPCQL1024 selected the option to create CvP Files is unavailable. 3 figures are attached to illustrate the situation.

Figure 2

Figure 3

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Do you enable the CvP in your PCIe IP setting? Could you share with me your sof file?

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi.

1st question on selecting EPCQL device for Cyclone 10 GX FPGA. This looks like a bug on Quartus 19.3 Pro Edition. This issue will be fixed in the next Quartus released. You can either select EPCQL with Arria 10 as the device or use Quartus 19.2.

For 2nd Question related to generating split perphi.jic and rbf file, you will need to add the sof file which has the the CvP initialization enabled before the "Create CvP File" is available to be enabled. This is to protect from accidentally enable and Quartus convert programming file generate error when user tried to convert it even if the sof file does not have CvP initialization enabled. Please let me know if you are still seeing the issue after adding the sof file into the Convert Programming File GUI.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

May I know if the generated sof file is with the CvP Initialization Enabled? May I know if you are able to share with me your sof file?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The .sof file is generated by the project compilation, the CvP initialization is unavailable as in the last Figure.