- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to make a state machine for controlling LEDs as tail lights are controlled on Ford Thunderbird. The board I'm using is DE0 Nano with Cyclone IV.

The state machine part is working fine, by simulation in Questa. Problem occurred when I realized I need clock with period around 0.5s to run that state machine.

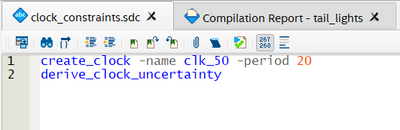

Board has 50MHz base clock so I made a component clk_divider, a simple counter that goes from 0 to 25000000 and then complements single-bit clk_reg which represents output of that divider. Also I made a sdc file to generate that virtual 50MHz clock for timing analysis. That clock is named clk_50 also as my main clock in state machine file(is that a problem maybe?).

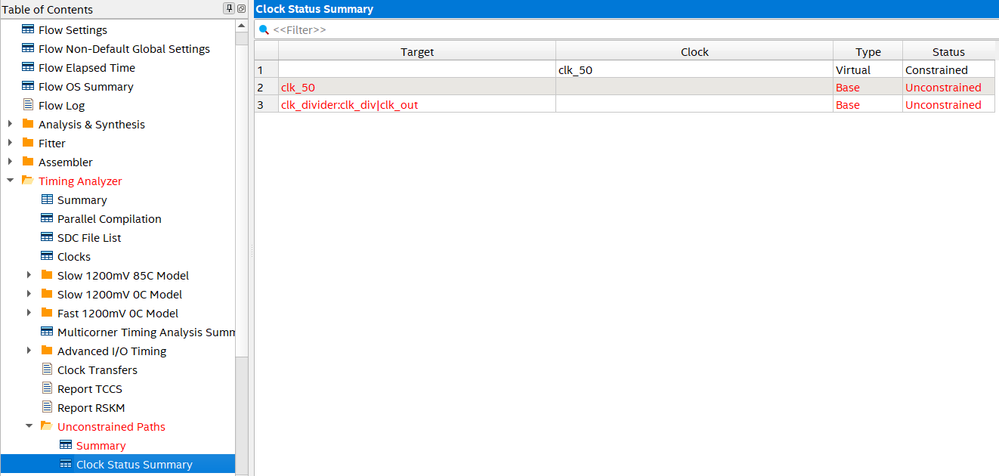

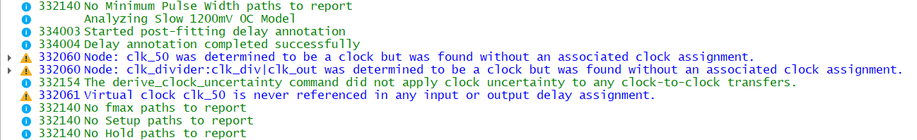

Now I'm stuck at Timing Analyzer and it says I have 2 unconstrained base clocks. When I put code on fpga it's working very strangely, e.g. when haz switch is on all lights are flashing but it seems like duty cycle of flashing is not 50% (haz is for Hazard meaning all lights should flash on-off). Other functionalities are not working at all.

Does unconstrained clocks maybe represent the problem why my design is not working or should I look for problem somewhere else?

Here is screenshot of error I'm getting and also files of my design.

- Tags:

- Timing Analysis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You created clk_50 as a virtual clock instead of a base clock because you didn’t set a target (typically with get_ports). Then you have to create a generated clock with the source as clk_50 and the target as the output of your clock divider and accurately describe the relationship between the two. You also should have input and output delay constraints for the I/O.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The one file you should have included here was your .sdc. This is not a high-speed design so missing timing constraints may not cause a problem with functionality, but you should still ensure your design is fully constrained.

Looking at your clock divider, though, you put clk_out in a separate process and put clk_reg in the sensitivity list with no code to define what happens when the process is activated by clk_reg toggling. That may be creating a latch. Remove clk_reg from the sensitivity list.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank You for your answer.

Tried removing clk_reg from sensitivity list in clk_reg_logic process and I'm still facing the same problem. I understand that clk_reg in sensitivity list of that process was not a need, because there's no event happening on clk_reg toggle.

Here's my .sdc file (filte type is not supported for upload, so there is a screenshot) and the screenshot of warnings I get while compiling this design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You created clk_50 as a virtual clock instead of a base clock because you didn’t set a target (typically with get_ports). Then you have to create a generated clock with the source as clk_50 and the target as the output of your clock divider and accurately describe the relationship between the two. You also should have input and output delay constraints for the I/O.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have generated real base clock and generated_clock that goes out of my clock divider and accurately described relationship between the two clocks. Also, I defined constraints for I/O. The design now works perfectly as I wanted it to work. From now on I will pay much more attention to timing analysis.

Thank You so much, this made my day!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page