- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am generating Trigger (500ns) and Counter data using Verilog code, whereas at every positive edge of trigger i am collecting and storing the data in register.

Verilog code

module Counter(

input clk,

input enable,

input reset,

output reg[31:0] Final_value,

output reg trig

);

reg[31:0] counter_out;

reg [7:0] temp=0;

reg [31:0] counter_result;

wire temp1;

wire edge_detect;

always@(posedge clk)

begin

if(reset)

begin

trig<=0;

temp<=0;

counter_out<=0;

end

else if (enable==1'b1)

begin

counter_out<=counter_out+1;

temp<=temp+1;

if(temp==25)

begin

temp<=0;

trig<=~trig;

end

end

end

assign temp1=trig;

assign temp2=temp1&&clk;

always@(posedge temp2)

if(reset)

counter_result<=0;

else

begin

counter_result<=counter_result+1;

end

always@(posedge trig)

if(reset)

Final_value<=0;

else

begin

Final_value<=counter_result;

end

endmoduleAltera Design as follows

- Counter module changed into block

- Interconnected with Qsys component

- Using FIFO, try to read the counter data

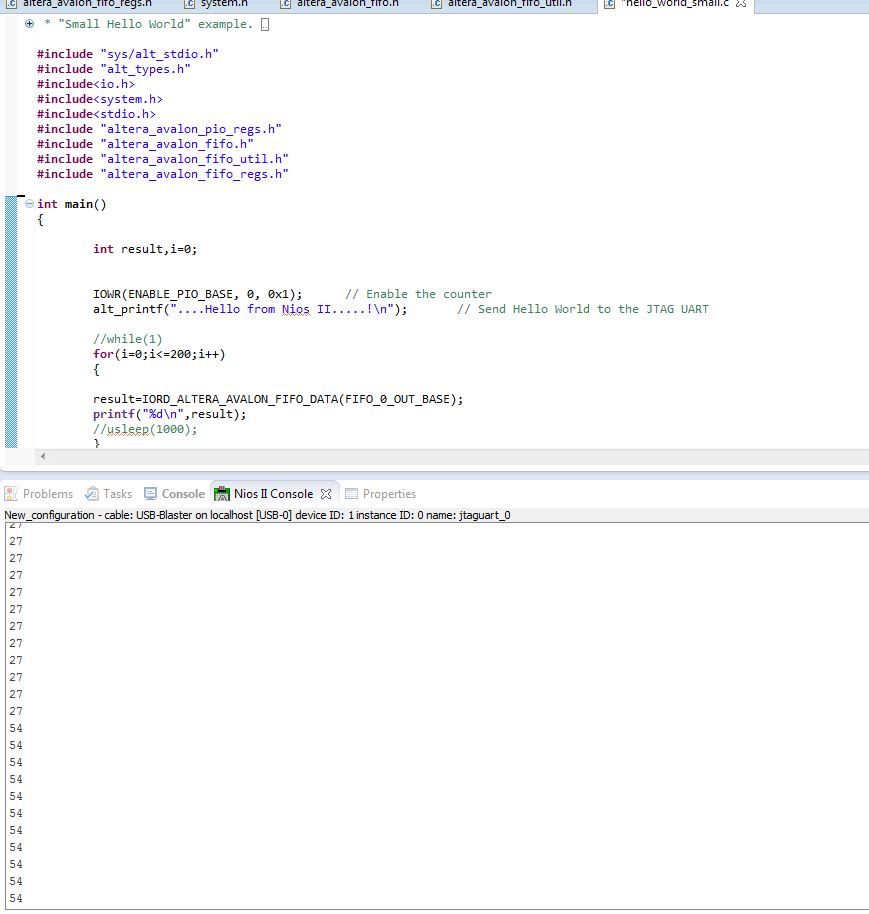

- Verifying the result in NIOS

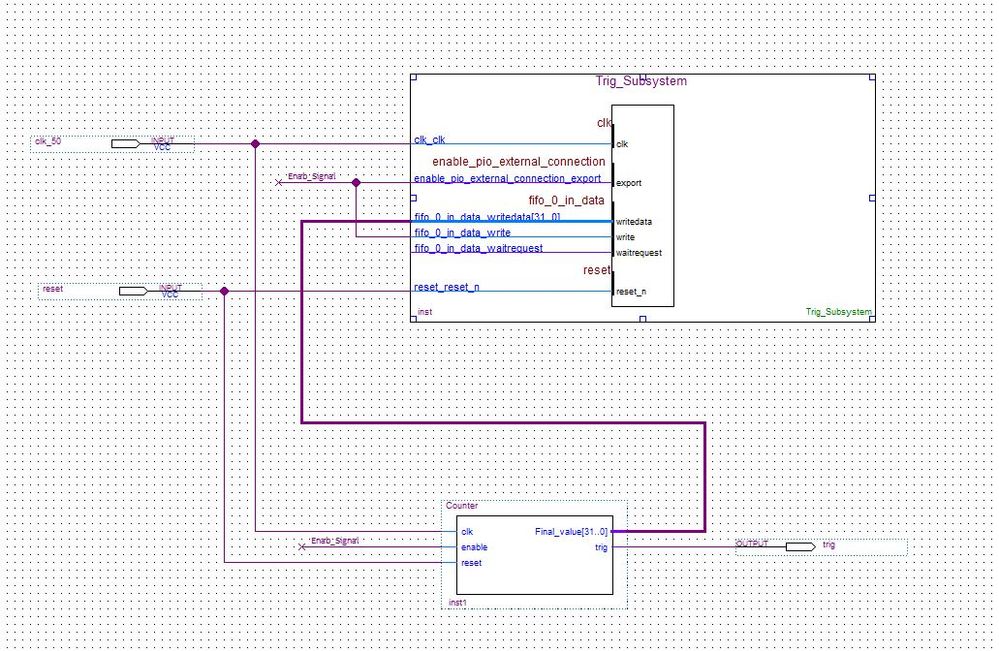

Top design

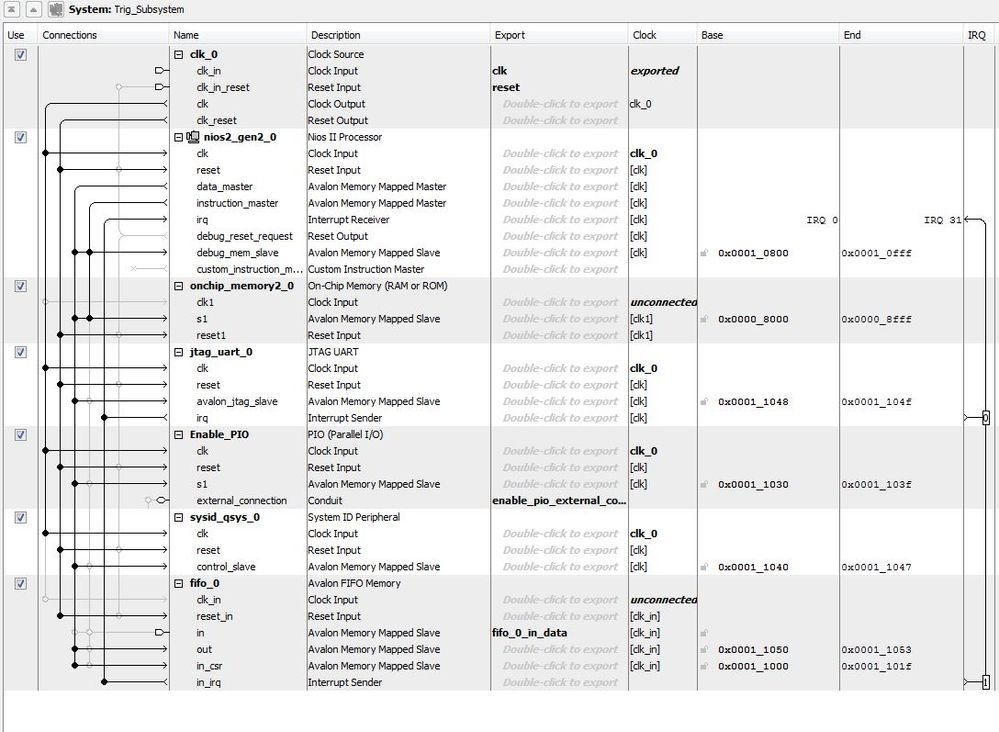

QSYS

IN NIOS , Data is repeating . I dont know why. can anyone please suggest me. Whether Verilog code logic is right.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Can you please review this part of code:

- always@(posedge clk)

- begin

- if(reset)

- begin

- trig<=0;

- temp<=0;

- counter_out<=0;

- end

- else if (enable==1'b1)

- begin

- counter_out<=counter_out+1;

- temp<=temp+1;

- if(temp==25)

- begin

- temp<=0;

- trig<=~trig;

- end

- end

- end

I see that after the first count is over if the reset signal didn't come the trig will stay high and there will be two counters are counting at the same time because (assign temp1=trig;) temp1 will be high and then the next counter will be enabled and counting with the clk

- always@(posedge temp2)

- if(reset)

- counter_result<=0;

- else

- begin

- counter_result<=counter_result+1;

- end

- always@(posedge trig)

- if(reset)

- Final_value<=0;

- else

- begin

- Final_value<=counter_result;

- end

I recommend to remove this assignment and try again

assign temp2=temp1&&clk;

or to change it to

assign temp2=temp1;

I know this isn't the desired system but just for debugging

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page