- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey, i got a question and i want to know if i did right.

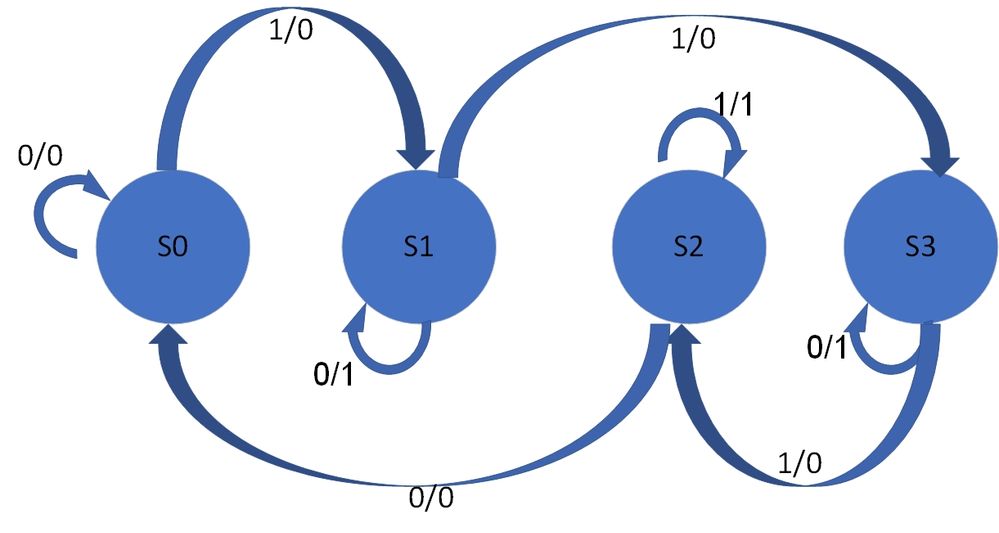

This is the Verilog code and i need to show the state diagram. this is what i did.

And this is the state. I think.

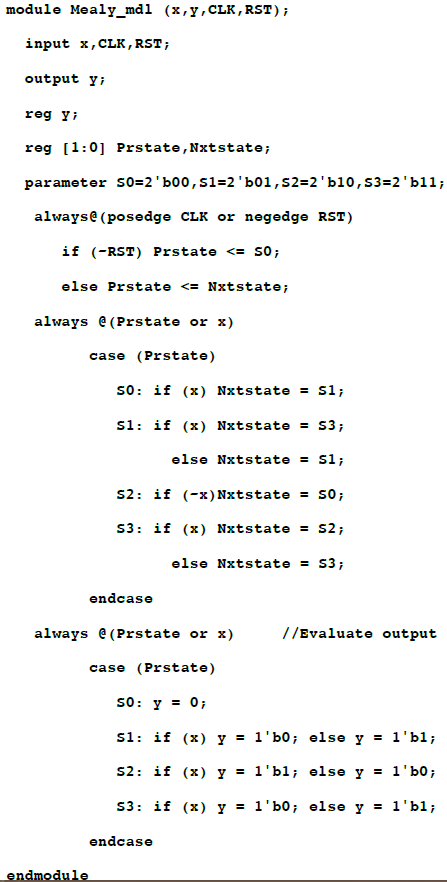

and the next question is, how can i convert this code from Mealy to Moore?

a clue please. a reference to youtube video or article. TY.

EDIT

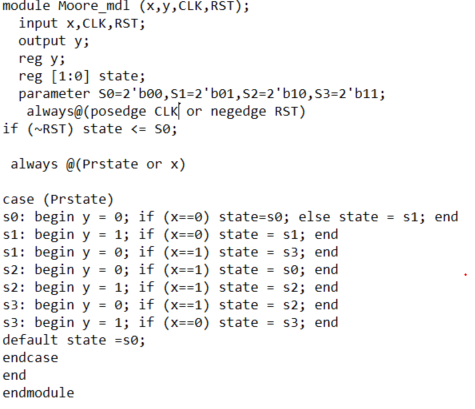

This is the Moore code

can someone tall me if this is correct?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok i see. And i`m doing this because this is the work we asked to do.

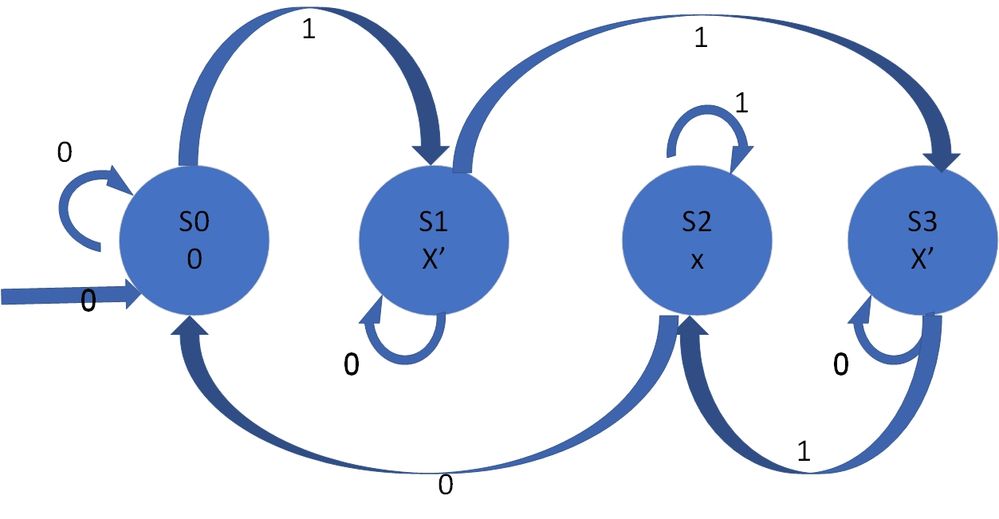

So i added the Moore Diagram, is this ok? and now i can convert it?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Looking at your Moore code, you shouldn't have two matching entries in a case statement, which Verilog might let you get away with, but you shouldn't do it.

But the design is inherently a Mealy state machine (dependent on the state and x), so I'm not sure why you want/need to turn it into a Moore machine.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What do you mean by "two matching entries"? you mean when i write

begin y = 0

and then y=1 for example? if does, how can i fix it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No, I mean you shouldn't have two identical entries in a case statement (two s1, two s2, two s3).

But as I said, there's no good way to fix this because the basic design is inherently a Mealy machine. What is your goal here and why do you want to change it into a Moore machine?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok i see. And i`m doing this because this is the work we asked to do.

So i added the Moore Diagram, is this ok? and now i can convert it?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page