- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

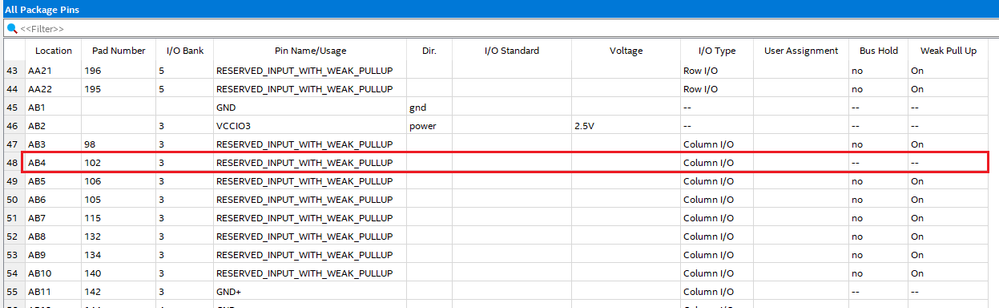

When compiling a Cyclone10 LP device, unused pins are set to “As input tri-stated with weak pull-up”.

Looking at the compiled report, the display is different only for unused VREFB pins.

Is Weak Pull Up enabled for this pin?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there

You can refer to .pin file on the connection for the unused pins. The .pin file will be generated after completion of the Fitter compilation.

You can also refer to link below:

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

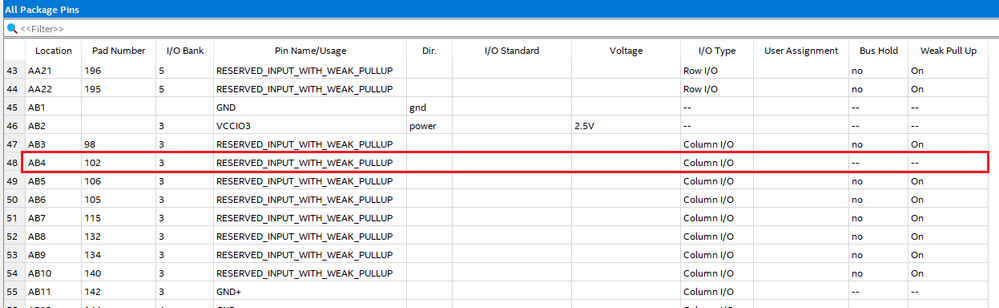

The pin number "AB4" enclosed in red is an unused VREFB pin. Is Weak Pull Up enabled?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

What view is this in Quartus tools?

As far as I understand, you could set the unused pin as shown here:

whereas the Weak Pull-Up Resistor shall be set through pin planner or assignment editor:

Both are different setting.

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there

I hope you are doing fine. We do not receive any response from you to the previous reply that have been provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Eng Wei

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page