- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

I am currently studying through the FPGA through Terasic DE2

I am using Quartus version 13.0spi.

Recently, I learned how to divide or multiply CLK using PLL.

I use Megawizard for this as it supports the process.

However, when setting the division factor or multiplier, the value is too small.

For example, when the division factor is 16, the value is maximum.

In other examples, there are cases where the division factor is 2500, but the maximum value in my case is too low.

Is the reason for this low value because I am using an old DE2 board? Or is it because the Quartus version is too old? Or is there any documentation related to this?

I have searched for answers but couldn't find an exact one.

Thank you for reading.

Dear. Sung zun

Ссылка скопирована

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

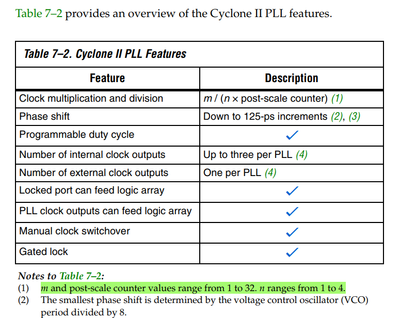

Megawizard setting reflect hardware features, in this case of Cyclone II PLL. Review device manual to learn about PLL structure and setting range of pre- and postdivider. Cyclone II postdivider has e.g. range of 1..32. Since Cyclone III, divider range is larger, the new devices also implement a feature to cascade dividers. If you need slower clock, you can implement divider in FPGA fabric.

Regards,

Frank

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi Dolemy,

As FvM said, you can refer to the "Chapter 7 PLL in Cyclone II Devices" in Cyclone® II Device Handbook to learn more about PLL architecture.

From Table 7.2 in this handbook, you can find out the highest division figure that PLL can provide. Further Restrictions could also be related to VCO frequency etc, which you can also find out in this chapter.

Some Intel FPGA devices' PLL can do "cascading", which makes a much higher Clock Division. But for Cyclone II device on this DE2 board, PLL cascading is not mentioned in the feature list. I will try in Quartus and see if it is possible to do cascading.

Cyclone® II Device Handbook: https://www.intel.com/content/www/us/en/content-details/654376/cyclone-ii-device-handbook.html?wapkw=cyclone%20II%20handbook&DocID=654376

Thanks & Regards,

Xiaoyan

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Thank you for your answer.

I read the Handbook according to your answer and solved the problem.

My problem was that cyclone ii supports a lower number of division and multiflier factors than I thought.

In the end, I added a separate circuit to my project to achieve my target clock

. Thanks to your answer, I was able to solve the problem. Thank you

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi there,

Good to know my answer helps!

By the way, we would appreciate it if you can take a moment to fill in the satisfaction survey. Your feedback is valuable and helps us improve our support quality.

Best regards,

Xiaoyan

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Of course!

But I don’t know where to do a survey.

Can you tell me how?

- Подписка на RSS-канал

- Отметить тему как новую

- Отметить тему как прочитанную

- Выполнить отслеживание данной Тема для текущего пользователя

- Закладка

- Подписаться

- Страница в формате печати