- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

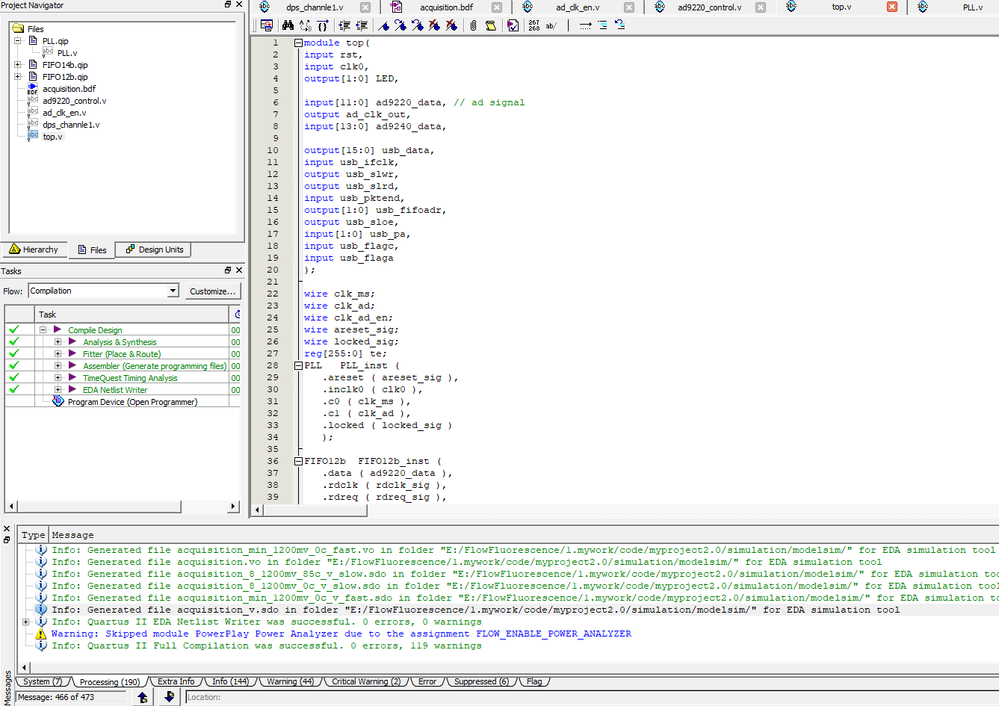

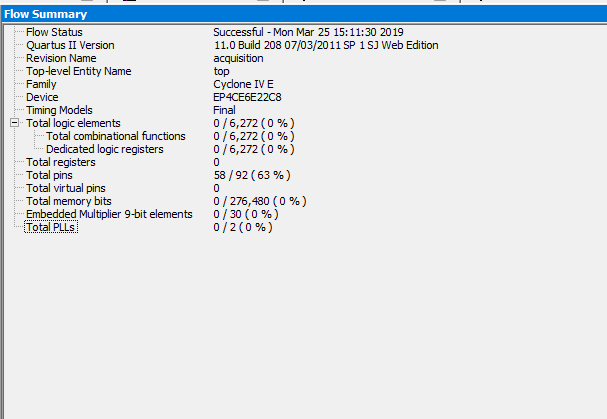

I used a PLL to produce clock, but it didn't display the resources usage when I made the verilog file as top file. But when i set the bdf file as top file it worked.

Is there any mistakes in my top verilog file though no error accour in the quartus? Waiting for your answers. Thanks a lot.

module top(

input rst,

input clk0,

output[1:0] LED,

input[11:0] ad9220_data, // ad signal

output ad_clk_out,

input[13:0] ad9240_data,

output[15:0] usb_data,

input usb_ifclk,

output usb_slwr,

output usb_slrd,

input usb_pktend,

output[1:0] usb_fifoadr,

output usb_sloe,

input[1:0] usb_pa,

input usb_flagc,

input usb_flaga

);

wire clk_ms;

wire clk_ad;

wire clk_ad_en;

wire areset_sig;

wire locked_sig;

reg[255:0] te;

PLL PLL_inst (

.areset ( areset_sig ),

.inclk0 ( clk0 ),

.c0 ( clk_ms ),

.c1 ( clk_ad ),

.locked ( locked_sig )

);

ad_clk_con ad_clk_enuser(clk_ad, clk_ad_en, ad_clk_out);

endmodule

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi 11000,

Synthesizer removes all logic whose outputs are unused.

You have have to route out some outputs otherwise the synthesizer will remove all of the logic.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi 11000,

Synthesizer removes all logic whose outputs are unused.

You have have to route out some outputs otherwise the synthesizer will remove all of the logic.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi AnandRS,

Thanks to your advice, I checked every module 's input and output pins the whole day. At last I made it out by ensuring every module has valid ports. It was really difficult for me to design the top file in verilog while my project had about ten modules. But I also think the bdf file would be complex and unclear in this situation.

Is there any better way for me to design the top file?

Thank you a lot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi 11000,

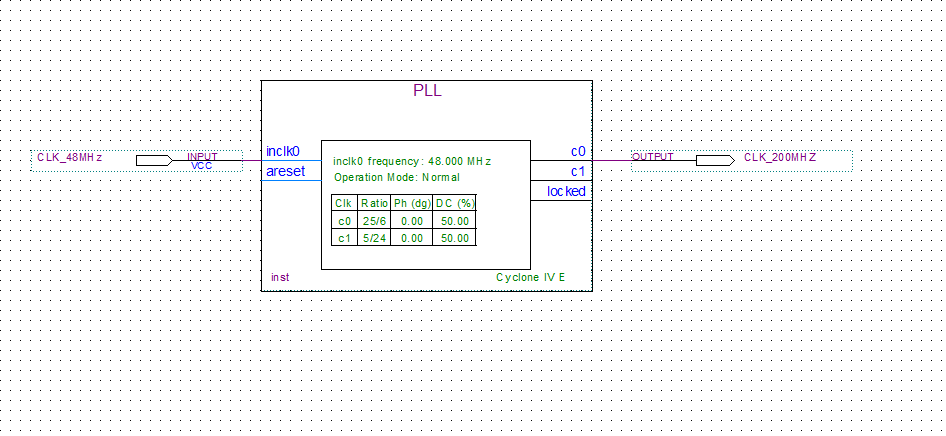

To view the resource you can add dummy ports in your module and connect it's output ports.

If we do so we can see 1-PLL being used.

Example:

`timescale 1 ps / 1 ps

module top (

input wire clk,

input wire reset,

//dummy ports

output wire locked_sig ,

output wire outclk_0

);

wire areset_sig ,clk_ms ,clk_ad;

PLL PLL_inst (

.areset ( areset_sig ),

.inclk0 ( clk),

.c0 ( clk_ms ),

.c1 ( clk_ad ),

.locked ( locked_sig )

);

endmoduleRegards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Connect the areset input pin to the PLL from the system rst and you can also use an internal wire for the locked pin

wire pll_locked;

PLL PLL_inst (

.areset ( rst ),

.inclk0 ( clk0 ),

.c0 ( clk_ms ),

.c1 ( clk_ad ),

.locked ( pll_locked )

);

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page