- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When we use old-version quaruts, say 15.0, we can put all the global `define statement in a seperate file , such as define.v ,add it to the file list, ant put it at first place to make sure it's seen by tool before it can see other .v files.

But when I tried to do the same thing in quartus 18, it doesn't work, quaruts keeps telling me my macros are not defined. unless i include my define.v in each .v file, which is ugly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hmm.. okay, let me clear the air regarding this.

First the 3 versions are different in the way they handle include files.

Lite / Std : We need to add the include files (be it with .v / .inc / .svh extension ) to the project and designate the top-level file. Then just compile. The tool automatically includes the defines / parameters file during compilation and it goes through.

Pro version : This version is modeled just like the industry ASIC compilers/synthesis tools. Here, even after we include the files into the file list, we still need to manually mention this include file in the design file using the `include <> compiler directive. This instructs the compiler to search for this file and include it during the compile process.

@Kevin Hsing .. I suggest you just add the `include "define.v" statement to the start of your design file. Make sure the path to the file is correct. If the define.v file is in the same folder as the source file, then its okay as is.. `include "deinfe.v"

This will include the file during compilation and you should not see those errors/warning.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Question is already discussed can you please check it maybe help full.

https://forums.intel.com/s/question/0D50P0000417fC1SAI/unable-to-synthesis-design-if-defines-are-included-in-seperate-file

Let me know if you need any further assistance.

Best Regards,

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've done this and it works in Quartus 18 Lite version. I've created a simple RAM design with a defines.v file that has the `defines in it. The tool picks up the defines and processes it accordingly.

// Single port RAM with single read/write address

module single_port_ram

#(parameter DATA_WIDTH=8, parameter ADDR_WIDTH=4)

(

input [(DATA_WIDTH-1):0] data,

input [(ADDR_WIDTH-1):0] addr,

input we, clk,

output [(DATA_WIDTH-1):0] q

);

`ifdef RTL

// Declare the RAM variable

reg [DATA_WIDTH-1:0] ram[2**ADDR_WIDTH-1:0];

// Variable to hold the registered read address

reg [ADDR_WIDTH-1:0] addr_reg;

always @ (posedge clk)

begin

// Write

if (we)

ram[addr] <= data;

addr_reg <= addr;

end

// Continuous assignment implies read returns NEW data.

// This is the natural behavior of the TriMatrix memory

// blocks in Single Port mode.

assign q = ram[addr_reg];

`else

ram_1port ram_1port_inst (

.address ( addr ),

.clock ( clk ),

.data ( data ),

.wren ( we ),

.q ( q )

);

`endif

endmoduleThis is the design file - single_port_ram.v and below is the defines.v file

`ifndef RTL

`define RTL

`endifAs you can see in the screenshot below, the compile goes through. I've done it for both with the RTL defined as well as without and get the intended results. I did mention the design file as Top-level entity via the Files tab and then just proceeded with the compile.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Abe

Thank you for your feedback.

I build a project and synthesis it using 18.0,it did works .

But I am using quartus18.0 pro(I'm evaluating stratix10 for my project, only 18.0pro support stratix10), same project failed. the tool gave me a critical warning, saying my macro not defined.

It seems Quartus18.0 pro and quartus18/quartus18-lite are totally different, their behavior when parsing rtl source code are quite different.

I tried the method your link provides,but it didn't work for me.

As I mentioned above, The problem only exist in quartus18-pro. quartus18/quartus18-lite works fine.

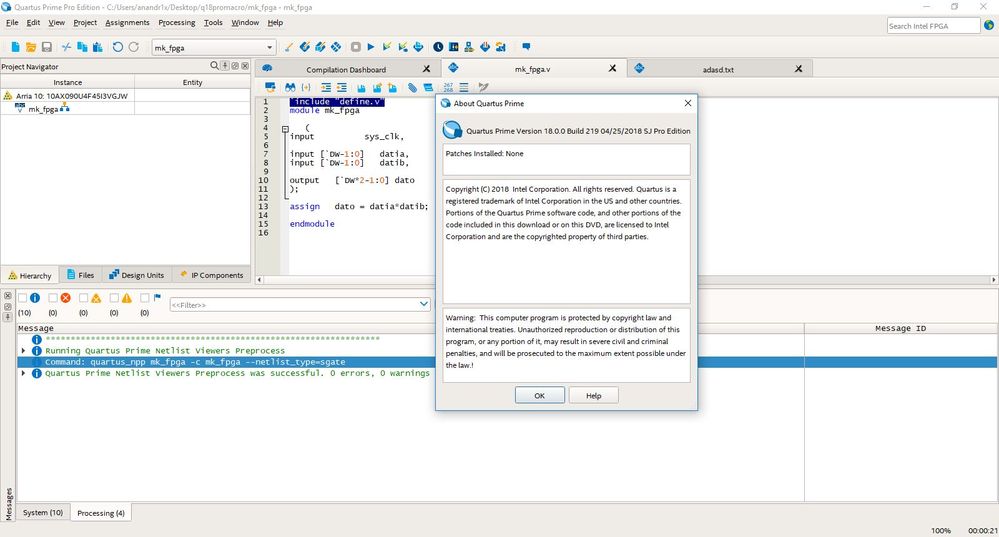

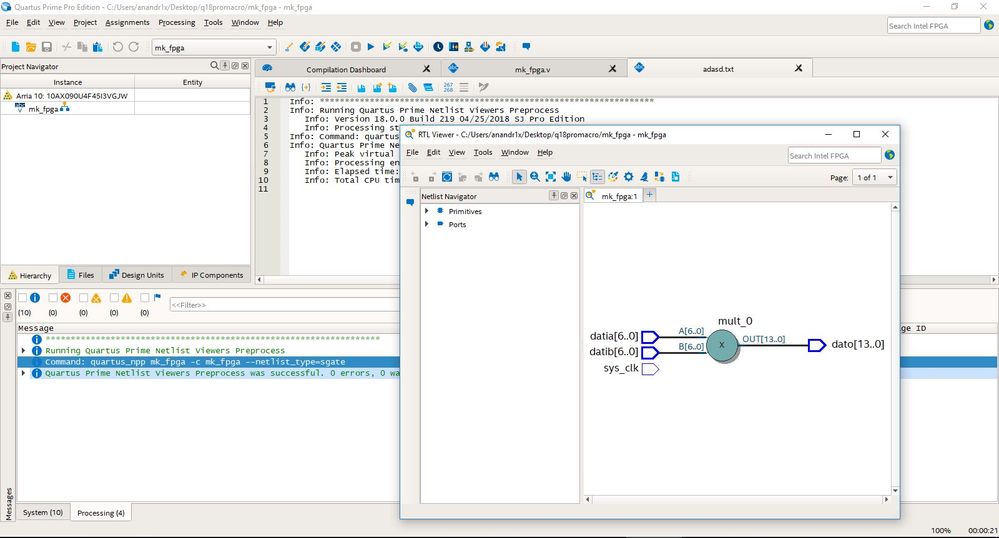

I enclose the source code and makefile for my project below:

//define.v

`ifndef MY_DEFINE

`define MY_DEFINE

`define DW 7

`endif//mk_fpga.v

module mk_fpga(

input sys_clk,

input [`DW-1:0] datia,

input [`DW-1:0] datib,

output [`DW*2-1:0] dato

);

assign dato = datia*datib;

endmodule#mk_fpga.tcl

# Load Quartus II Tcl Project package

package require ::quartus::project

load_package flow

set need_to_close_project 0

set make_assignments 1

# Check that the right project is open

if {[is_project_open]} {

if {[string compare $quartus(project) "mk_fpga"]} {

puts "Project mk_fpga is not open"

set make_assignments 0

}

} else {

# Only open if not already open

if {[project_exists mk_fpga]} {

project_open -revision [lindex $argv 0] mk_fpga

} else {

project_new -revision [lindex $argv 0] mk_fpga

}

set need_to_close_project 1

}

# Make assignments

if {$make_assignments} {

set_global_assignment -name VERILOG_FILE define.v

set_global_assignment -name VERILOG_FILE mk_fpga.v

}

# Commit assignments

export_assignments

puts "++++++ assignment complete"

execute_flow -compile

# Close project

if {$need_to_close_project} {

project_close

} #makefile

PRJ_NAME=mk_fpga

DATE=`date +%y%m%d_%H%M`

#quartus18.0 pro

q18p:

/home/opt/intelFPGA_pro/18.0/quartus/bin/quartus_sh -t $(PRJ_NAME).tcl $(PRJ_NAME)

#quartus18.0

q18s:

/home/opt/intelFPGA/18.0/quartus/bin/quartus_sh -t $(PRJ_NAME).tcl $(PRJ_NAME)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, somehow the Quartus Pro version does not treat the include files / defines.v files the same way as it does in the Lite and Standard versions. It just doesn't read the defines file and take in the value. Looks like the only way to work around this is to declare all the defines in the design file itself. Maybe Intel folks need to help us on how to get this done with the Pro version.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Abe

IT'S NOT A BUG.

If you would tried the link which i have shared, It would have solved your problem.( we verify answer before providing it).

- Quartus pro 18.0 works well with macros in separate file or in same file.

- I have verified with your design in quartus version(17.1,18,18.1) and edition(Lite & pro) & It read the defines file and take in the value, but you have to add `include "define.v" line in it design.

Attached the documents with images.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Best Regards,

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well, I did noticed inserting `include define.v in each of my .v file can solve my problem.

My project has hundreds of .v, although I can complete the insertion task using a shell script, still I don't think it's a graceful solution, since all other eda tools I use don't require such coding style including quaruts 18.0 standard version, It seems it's a new requirement of quartus-pro series code parser.

If there is no other work-around such as using a global assignment to inform the tool such file should be read first and all the macros in it be considered global, I'll just add `include statement to continue my evaluation.

Still, I hope quartus pro's behavior is consistant with quartus standard series and other eda tools.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hmm.. okay, let me clear the air regarding this.

First the 3 versions are different in the way they handle include files.

Lite / Std : We need to add the include files (be it with .v / .inc / .svh extension ) to the project and designate the top-level file. Then just compile. The tool automatically includes the defines / parameters file during compilation and it goes through.

Pro version : This version is modeled just like the industry ASIC compilers/synthesis tools. Here, even after we include the files into the file list, we still need to manually mention this include file in the design file using the `include <> compiler directive. This instructs the compiler to search for this file and include it during the compile process.

@Kevin Hsing .. I suggest you just add the `include "define.v" statement to the start of your design file. Make sure the path to the file is correct. If the define.v file is in the same folder as the source file, then its okay as is.. `include "deinfe.v"

This will include the file during compilation and you should not see those errors/warning.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page