- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone, I'm struggling to solve an issue inside my Modelsim simulation.

I have my testbench written in VHDL, which instantiates a component written in VHDL as well (the UUT), and a simulation model written in Verilog (which I found online).

The UUT and the simulation model share a bidirectional line which is pulled-up high ('H', but I tried to use 'Z' as well). While the UUT manages to take control of the line and output '0's and '1's, the simulation model just can't. I also put breakpoints in the code and verified that, internally to the Verilog file, it tells me that the line is actually assigned "St0" or "St1".

The fact is, when I watch in my "Wave" tab, I see that the line sticks on 'H' (same with 'Z').

So, my question is: am I missing something? Is there a setting to select somewhere to help the simulation model to put the right values on the shared line? I've never made a mixed-HDL simulation so I hope someone can give me a hand.

Thank you very much,

Vince.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Without seeing any code or the waveform, it's very hard to understand what's happening here. Can you post something?

Sidenote: you can't use bidirectional signaling internally to the FPGA, only on I/O. There is no internal bidirectional logic. It's not clear where the bidi you're talking about is located, so I just thought I'd put that here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, thanks for your reply.

My UUT is the top-level of the FPGA, so it's fine to have bidirectional pins. I set them to 'H' in my testbench in order to simulate the pull-up resistors on the board.

I'm developing a tiny Secure Digital host, the CMD and DAT lines are bidirectional, while the CLK line goes from the host to the card. CMD and DAT lines are put to 'Z' when they are not used, while the tristate port is enabled when a command, a response, a read or a write is performed.

I found the simulation model of the card online, it was in a very well done project. Moreover, using the breakpoints in Modelsim I verified that it works. It just can't "win" the 'H' in the testbench for some reason.

The code:

sd_host_inst : component sd_host port map (

...

SD_CLK => SD_CLK,

SD_CMD => SD_CMD,

SD_DAT => SD_DAT

);

SD_CMD <= 'H';

SD_DAT <= (others => 'H');

sd_card_inst : component sd_card port map (

SD_CLK => SD_CLK,

SD_CMD => SD_CMD,

SD_DAT => SD_DAT

);

Thanks again,

V.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

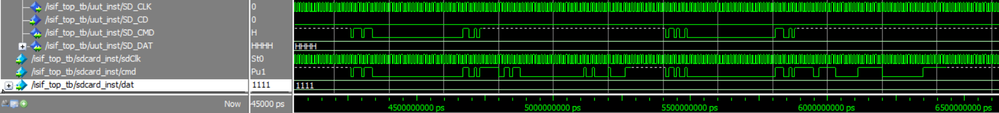

I attached the waves: the first 3 are relative to the UUT, the others to the simulation model. As you can see, the simulatiom model replies on the CMD line internally, but this reply can't arrive to the UUT for some reason:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vincenzo,

You can use RTL viewer and Technology map to analyze and debug your design. You may have to check your RTL for intended function is correctly made or otherwise.

Thanks,

Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page