- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

I am creating a PCIe controller targeting Agilex F series device. Wanted to run the example design on Cadence Xcelium simulator. When I ran the generated script for Xcelium, I got the below error:

- xmsim: *F,NOSNAP: Snapshot 'pcie_ed_tb.pcie_ed_tb' does not exist in the libraries.

When I searched the Intel knowledge base, I came across the link R-tile Xcelium fix.

Guess this has been fixed for P-tile devices as well. But I also found the below message in the link.

- Note: The Xcelium simulator support is only available in devices with the suffix R2 or R3 in their ordering part numbers (OPNs).

Does this mean Xcelium is not fully supported for P-Tile or R-Tile Simulations? Will there be a fix in future? Btw. I am running Quartus 23.1 Pro.

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

Apologies for the delay in responding to your prior follow-up email.

Yes, you can close this ticket.

Thank you for the support.

Regards

Binu

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If refer to the latest version of User Guide

https://www.intel.com/content/www/us/en/docs/programmable/683059/23-2-9-0-2/features-83772.html

- Riviera*, Siemens EDA QuestaSim* and VCS* are the simulators supported in the 22.2 (or later) release of Intel® Quartus® Prime. Other simulators may be supported in a future release.

That means you can't use Xcelium to simulate P-tile PCIe IP now. The simulation error is expected.

Regards

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I wish to follow up with you about this case.

Do you have any further questions on this matter ?

Else I would like to have your permission to close this forum ticket

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

Thank you for following up.

I still would like to have more clarity on what I have understood so far. From what I see, there is NO Xcelium support for P-Tile IP as you pointed out. But I came across the limited Xcelium support on R-Tile based devices at https://www.intel.com/content/www/us/en/docs/programmable/683501/23-2-10-0-0/features.html

I also see that the AGI027 Agilex board may be populated with one of 2 devices(AGIB027R29A1E2VR3 or AGIB027R29A1E1VB) as mentioned in https://www.intel.com/content/www/us/en/products/details/fpga/development-kits/agilex/agi027.html. Are you able to advise which device gets populated on this board? Is it based on customer request or part availability?

The reason I am asking this is, if AGI027 gets populated with AGIB027R29A1E2VR3, I believe Xcelium will be supported for that device/board as it matches the highlighted item/OPN in below screenshot.

Regards

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes you are right.

If for R-tile it did support as per mention in the user guide in the latest version of Quartus

But for P-tile, it may be supported in future releases (Subject to change), so the error you see in P-tile is expected.

Let me know if you need any further clarification.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Looks like you missed couple of questions from my previous message. Please see the highlighted section from below screenshot. Could you clarify those?

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If I understand your question correctly on below

Does this mean Xcelium is not fully supported for P-Tile or R-Tile Simulations? Will there be a fix in future? Btw. I am running Quartus 23.1 Pro.

>> if refer to the latest user guide of P-tile it is not supported Xcelium simulation at the moment. Please consider to user other that is supported.

>> For R-tile, if refer to the user guide, it support for specific device/board with listed OPN as what you shows to me.

Are you able to advise which device gets populated on this board? Is it based on customer request or part availability?

I also see that the AGI027 Agilex board may be populated with one of 2 devices(AGIB027R29A1E2VR3 or AGIB027R29A1E1VB)

>> I not understand your question, what do you mean by which device gets populated on this board ?

I believe Xcelium will be supported for that device/board as it matches the highlighted item/OPN in below screenshot.

>> Yes, your understanding is correct

Regards

Wei Chuan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wei,

Please see my responses marked [Binu]

Question: I also see that the AGI027 Agilex board may be populated with one of 2 devices(AGIB027R29A1E2VR3 or AGIB027R29A1E1VB)

>> I not understand your question, what do you mean by which device gets populated on this board ?

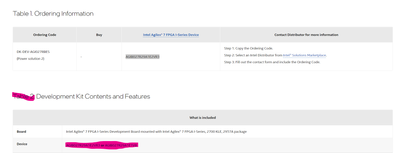

[Binu] I specifically asked this as the FPGA device mentioned in the link has 2 devices mentioned in Table2. The two devices are AGIB027R29A1E2VR3 or AGIB027R29A1E1VB. Table 1 only mentions one device AGIB027R29A1E2VR3. Please see link AGI027 eval kit and below screenshot for reference.

Question: I believe Xcelium will be supported for that device/board as it matches the highlighted item/OPN in below screenshot.

>> Yes, your understanding is correct

[Binu] Today I hit the same error when I tried generating R-Tile IP targeting AGIB027R29A1E2VR3 and ran the Xcelium simulation. I am using Quartus Pro 23.1 and the 23.1 document says this device is supported.

- xmsim: *F,NOSNAP: Snapshot 'pcie_ed_tb.pcie_ed_tb' does not exist in the libraries.

Hope this clarifies my queries.

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wei,

Please see my responses marked [Binu]

Question: I also see that the AGI027 Agilex board may be populated with one of 2 devices(AGIB027R29A1E2VR3 or AGIB027R29A1E1VB)

>> I not understand your question, what do you mean by which device gets populated on this board ?

[Binu] I specifically asked this as the FPGA device mentioned in the link has 2 devices mentioned in Table2. The two devices are AGIB027R29A1E2VR3 or AGIB027R29A1E1VB. Table 1 only mentions one device AGIB027R29A1E2VR3. Please see link AGI027 eval kit and below screenshot for reference.

Question: I believe Xcelium will be supported for that device/board as it matches the highlighted item/OPN in below screenshot.

>> Yes, your understanding is correct

[Binu] Today I hit the same error when I tried generating R-Tile IP targeting AGIB027R29A1E2VR3 and ran the Xcelium simulation. I am using Quartus Pro 23.1 and the 23.1 document says this device is supported.

- xmsim: *F,NOSNAP: Snapshot 'pcie_ed_tb.pcie_ed_tb' does not exist in the libraries.

Hope this clarifies my queries.

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

[Binu] I specifically asked this as the FPGA device mentioned in the link has 2 devices mentioned in Table2. The two devices are AGIB027R29A1E2VR3 or AGIB027R29A1E1VB. Table 1 only mentions one device AGIB027R29A1E2VR3. Please see link AGI027 eval kit and below screenshot for reference.

>> the OPN end with R3 is the latest silicon build, while the other is initial build.

If you need more information, you can contact the distributor/sales for the product specification.

[Binu] Today I hit the same error when I tried generating R-Tile IP targeting AGIB027R29A1E2VR3 and ran the Xcelium simulation. I am using Quartus Pro 23.1 and the 23.1 document says this device is supported.

- xmsim: *F,NOSNAP: Snapshot 'pcie_ed_tb.pcie_ed_tb' does not exist in the libraries.

>> yes, if refer to the user guide, it shall be supported. Can you please provide me the

1. Design .qar file

2. Printscreen of the error

I will file this to the development team, meanwhile can you try to generate a clean project and try it again if you seeing the same error ?

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

Thank you for the reply. I cleaned the project but that did not help. But I realised I missed some of the arguments/environment variables mentioned in https://www.intel.com/content/www/us/en/docs/programmable/683544/22-2-6-0-0/simulator-43921.html . Simulation seems to progress and looks like IP component was identified. But simulation was hanging after half an hour. So I kicked off again. Will let you know how that goes.

Do you know how long the simulation takes? Any ball park figure like 30 minutes, 1hour, 2hour?

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

I check the internal document, by right R-tile with R3 OPN shall able to run simulation and it is supported.

I do not have the exact simulation time for this, but is shall be less than 2 hours for normal use, however in some case and situation if the design is large, it might take more time.

Regards,

Wincent_intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

Thanks for confirming the R-Tile Xcelium support. I should have clarified regarding simulation time.

My question was regarding simulation time of the provided PIO example design. To give you context, I crated the R-Tile IP for AGIB027R29A1E2VR3 in below PCIe mode:

- 1x16, 1024, TLP Bypass downstream

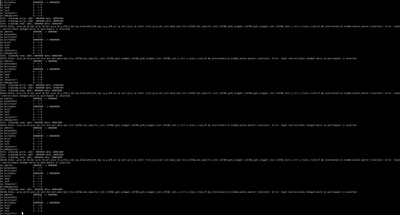

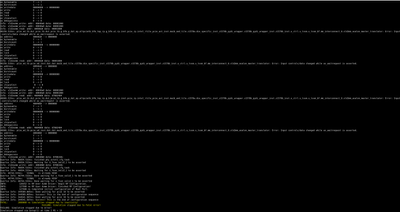

When I ran simulation, I can see it no longer reports the previous error and proceeds to simulation, but the simulation got hung at a particular point(screenshot below for reference). I cleaned project and re-ran couple of times and had the same issue. The simulation has been hanging now for more than 10 hours.

Could you check with your development team regarding this? Basically, I want to have a confirmation that this hanging issue is not due to any Xcelium compatibility with the OPN.

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

For the PIO design example simulation, by right you shall see

"Simulation stopped due to successful completion"

Can you please check back the user guide and ensure that you do not miss any step on that ?

https://www.intel.com/content/www/us/en/docs/programmable/683544/22-2-6-0-0/steps-to-run-simulations.html

Also, I would like to recommend you try out other simulation tools if you have time.

The step is to narrow down the problem that you are seeing.

Besides, that can you try the simulation using Quartus v23.2 ?

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

Yes I am aware that I should see "Simulation stopped due to successful completion". I did not see that and hence concerned/mentioned in this ticket.

I repeatedly reviewed and done the steps mentioned in https://www.intel.com/content/www/us/en/docs/programmable/683544/22-2-6-0-0/simulator-43921.html.

We do not have other simulators in our environment and hence unable to try anything other than Xcelium.

Trying Quartus v23.2 is in my list today. But as per User Guide v23.1 is also supported. Anyways will try v23.2 today.

Regards

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

Thanks for that,

We have some update in the newest version of Quartus, I am not sure that this able to solve the issue you seeing.

But the good start is you not seeing the earlier error anymore.

if you still seeing the same error using v23.2. Please sent me the .qar file together with any testbench file.

I will file this to related team.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

I was finally able to get the simulation finishing and passing in Quartus 23.2_pro. So we will upgrade our internal version to 23.2_pro. I had to also put the IP in Gen5, 1x16, 1024 bit mode. Looks like that is one of the only 2 modes supported by example design.

Finally, I have couple of additional questions.

- Can you check and confirm if there are any fundamental functionality differences between a P-tile and R-tile IP?

- Say for example, if I generate a R-tile IP in Gen3,2x8 mode with TLP header enabled in GUI and this works in simulation, can I replace it with a P-tile Gen3, 2x8 mode IP later if needed and expect same functionality?

- Related to the above question, is the R-tile IP interface backward compatible to a P-tile IP interface?

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

Glad that you are able to simulate the R-tile design.

For P-tile as refer to my previous reply, the Xcelium is not available at the moment if refer to the P-tile latest version of user guide.

For the backward compatible issue, you can refer the below for more detail

Let me know if further clarification is needed.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

OK. I am getting clarity on the backward compatibility. There are two things I see:

- enabling the Header checkbox from R-tile IP GUI gives a P-tile style (big endian) header

- The pins are not exactly backward compatible as per the above link as the R-tile ports have "st" marking

Going back to my Question 1:

- Can you check and confirm if there are any fundamental functionality differences between a P-tile and R-tile IP?

- Say for example, if I generate a R-tile IP in Gen3,2x8 mode with TLP header enabled in GUI and this works in simulation, can I replace it with a P-tile Gen3, 2x8 mode IP later if needed and expect same functionality?

Can you confirm despite the minor pin name differences, whether functionality of P-tile vs R-tile for a particular Gen of PCIe remains the same?

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For your question 1, for sure there is some difference between P-tile and R-tile IP.

For example some of the pin assignment, pin name, and some adding features such as PIPE direct mode.

I do not recommend you to simply generate any design and replace it with P-tile.

But theoretically, you can do it, but we never test it on our place before.

for the fundamental different, you can refer to

https://www.intel.com/content/www/us/en/products/details/fpga/intellectual-property/interface-protocols/pcie-p-tile-hard-ip.html

Regards,

Wincent_Intel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page