- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i synthesis my design at synplify pro and then i fetched the VQM netlist and start fitting the design at Quartus. i got an error that there are two bits in a module at the design it can not be fit at the design i tried alot of fitting options but there is no solution

FPGA is not fully utilized and i didn't see anything wired at the two bits that the tool said

Thanks in advance

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That Cyclone V (or Quartus) has so many problem to route signals ...

I never seen such routing issue with any other FPGA's ...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Check out these two previous similar forum issues probably can help you.

May check on the link below as well.

CAUSE: The Fitter was unable to route the design because it requires too many device routing resources.

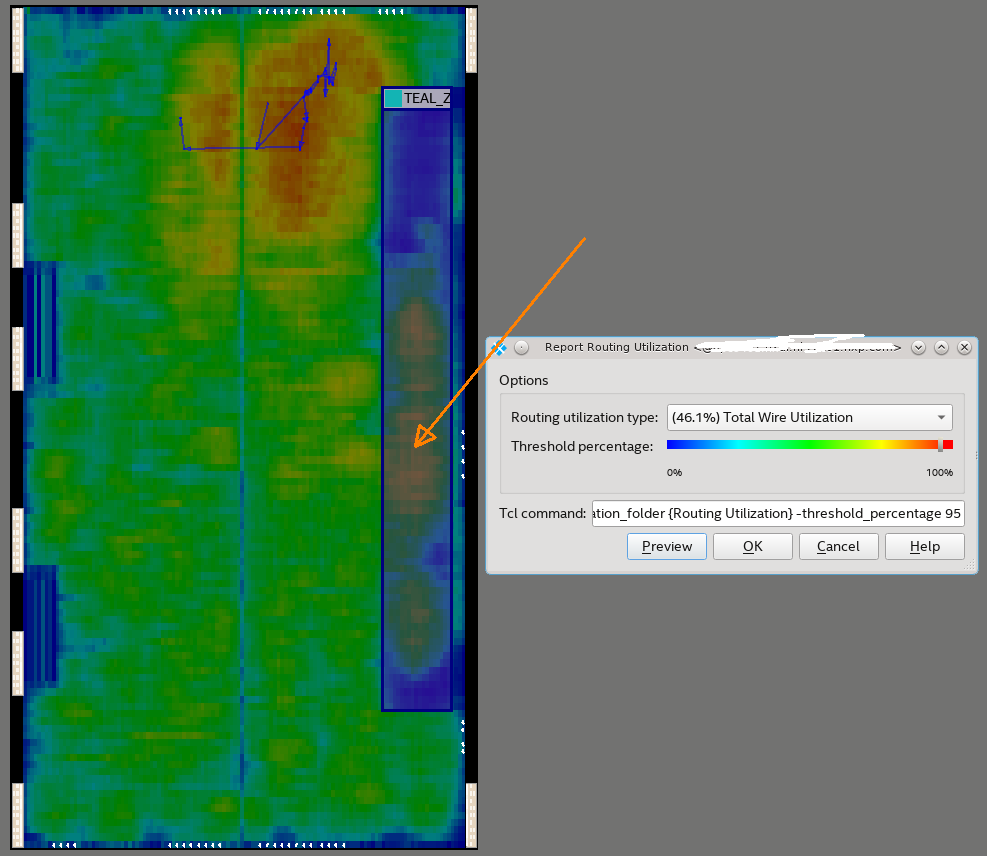

- View the Global Routing Wire Utilization Map in GUI for overall routing congestion.

- View the Report Routing Utilization in Chip Planner for detailed routing congestion.

- Investigate signals identified by the router.

- Turn off timing optimization or alternatively just hold optimizations to see if timing constraints are the issue.

- Investigate non-global large fanout nets.

- Reduce routing demand by modifying the design. Reduce the interconnect complexity by localizing routing as much as possible. For example, transform a cross-bar interconnect into a ring-style interconnect to reduce interconnect complexity and improve routability (at the cost of increasing latency).

- If a global signal is unroutable, then delete global promotion of that signal.

- Add or remove Logic Lock regions.

- Reduce very aggressive timing constraints.

- Cut timing paths on cross-clock transfers.

- Change the Fitter Initial Placement Seed in the Advanced Fitter Settings dialog.

- Enable the Fitter Aggressive Routability Optimizations logic option in the Advanced Fitter Settings dialog.

- Reduce logic utilization.

- Select a larger device.

Best Regards,

Sheng

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution and give Kudos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May I know any update? Do the suggestions help?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Still difficult to route using different actions like mentioned above but I can work with.

Either the Cyclone V has limited routing capabilities, either Quartus has a bug.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have you try with below compiler settings before:

OPTIMIZATION_TECHNIQUE AREA (Balanced to Area)

OPTIMIZATION_MODE "AGGRESSIVE AREA"

SYNCHRONIZATION_REGISTER_CHAIN_LENGTH 2 (3 to 2)

ALLOW_SHIFT_REGISTER_MERGING_ACROSS_HIERARCHIES ALWAYS (Auto to Always)

PHYSICAL_SYNTHESIS_REGISTER_DUPLICATION OFF (ON to OFF)

Allow Register Duplication (Off)

Remove Duplicate Registers (On)

Auto Register Duplication (Off)

Logic Cell Insertion - Logic Duplication (Off)

Perform Register Duplication for Performance (Off)

Fitter Aggressive Routability Optimizations (Always)

Auto Packed Registers (Minimize Area with Chains)

Optimize IOC Register Placement for Timing (Pack All IO Registers)

Perform Logic to Memory Mapping for Fitting (On)

Check also chip planner as well must be some place highly hotspot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OPTIMIZATION_TECHNIQUE AREA (Balanced to Area) => tested already

OPTIMIZATION_MODE "AGGRESSIVE AREA" => tested already

SYNCHRONIZATION_REGISTER_CHAIN_LENGTH 2 (3 to 2) => NOT tested, will try it

ALLOW_SHIFT_REGISTER_MERGING_ACROSS_HIERARCHIES ALWAYS (Auto to Always) => NOT tested, will try it. Note that my main netlist is from Synplify .vqm and that the congestion is in the cortex M33 in that netlist.

PHYSICAL_SYNTHESIS_REGISTER_DUPLICATION OFF (ON to OFF) => tested already

Allow Register Duplication (Off) => tested already

Remove Duplicate Registers (On) => tested already

Auto Register Duplication (Off) => tested already

Logic Cell Insertion - Logic Duplication (Off) => tested already

Perform Register Duplication for Performance (Off) => tested already

Fitter Aggressive Routability Optimizations (Always) => tested already

Auto Packed Registers (Minimize Area with Chains) => tested already

Optimize IOC Register Placement for Timing (Pack All IO Registers) => NOT tested, will try it

Perform Logic to Memory Mapping for Fitting (On) => NOT tested, will try it

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

There is only optimization mode.

Also, may be you can use larger capacity cyclone v device with more ALMs, Total I/Os, GPIOs, Memory Bits, DSP Blocks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

What do you mean by "There is only optimization mode."

We already use the biggest Cyclone V and we won't change it anyway.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

These are the closest .qsf accepted values I found for the Cyclone V and Quartus 21.1.0 std version:

set_global_assignment -name CYCLONEII_OPTIMIZATION_TECHNIQUE AREA

set_global_assignment -name OPTIMIZATION_MODE "AGGRESSIVE AREA"

set_global_assignment -name SYNCHRONIZATION_REGISTER_CHAIN_LENGTH 2

set_global_assignment -name ALLOW_SHIFT_REGISTER_MERGING_ACROSS_HIERARCHIES ALWAYS

set_global_assignment -name PHYSICAL_SYNTHESIS_REGISTER_DUPLICATION OFF

set_global_assignment -name ALLOW_REGISTER_DUPLICATION OFF

set_global_assignment -name REMOVE_DUPLICATE_REGISTERS ON

set_global_assignment -name ROUTER_REGISTER_DUPLICATION OFF

set_global_assignment -name ROUTER_LCELL_INSERTION_AND_LOGIC_DUPLICATION OFF

set_global_assignment -name FITTER_AGGRESSIVE_ROUTABILITY_OPTIMIZATION ALWAYS

set_global_assignment -name QII_AUTO_PACKED_REGISTERS "MINIMIZE AREA WITH CHAINS"

set_global_assignment -name OPTIMIZE_IOC_REGISTER_PLACEMENT_FOR_TIMING "PACK ALL IO REGISTERS"

set_global_assignment -name INFER_RAMS_FROM_RAW_LOGIC ON

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you provide the .fit.rpt for taking a look?

Thank you,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Let me know how to send it in private.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You could provide the fitter report personally to me via this email id qi.sheng.ng@intel.com

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After going through the fitter report, looks like still not that extremely compact yet should be not a problem for routing.

Btw, glad to know that you have successfully route the design after a retry.

Thank you,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the logic lock region in blue , when it fails to route the Cortex M33, there are high wire utilization.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The Compiler's messages contain information about average and peak interconnect usage. Peak interconnect usage over 75%, or average interconnect usage over 60%, can indicate difficulties fitting your design. Similarly, peak interconnect usage over 90%, or average interconnect usage over 75%, show increased chances of not getting a valid fit.

Based on the picture, I think your design should be no problem at routing for the time being.

Do let me know if you need any further help on this.

Thank you,

Sheng

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page