- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am using Quatus Prime Lite 17.1. In Nios II build tool for eclipse, two files were made, "embed" and "embed_system.bsp", of which the build project was done successfully. However, to build project of "embed" failed with errors as followed:

"#error Your SystemID peripheral must be named exactly "sysid" in your SOPC Builder system. Please check that you have properly constructed your system before compiling this program.

^

inc/system_validation.h:32:6: error: #error Your JTAG UART peripheral must be named exactly "jtag_uart" in your SOPC Builder system. Please check that you have properly constructed your system before compiling this program.

#error Your JTAG UART peripheral must be named exactly "jtag_uart" in your SOPC Builder system. Please check that you have properly constructed your system before compiling this program.

^

make: *** [obj/default/main.o] Error 1

20:43:28 Build Finished (took 2s.537ms)"

In the Platform Designer (SOPC Builder system). These names "sysid" and "jtag_uart" were used as the error messages suggested. What are the problems and the solution?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Could you try using the Nios II SBT design template, and select the Hello World template. Then, you should regenerate a new BSP to see the mismatch of names come from the new BSP, or you were using the old BSP generated with the wrong name.

Also, what is the FPGA development kit you are using for your project?

Hope this helps.

Thank you.

Regards.

Kelly

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Did you try regenerating your system in Platform Designer to create an updated .sopcinfo file? Perhaps the build tools are seeing old info.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, once the suggested corrections were made in the Design Platform. The new system was generated in Design Platform and a full compilation in Quartus Prime Lite was done successfully. Then the eclipse was performed, still the same errors messages appeared.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Greetings and Welcome to Intel's forum.

You may follow the steps in the embedded design handbook to add the system ID peripheral at section 3.6.5.5.6. (Add the System ID Peripheral): https://www.intel.com/programmable/technical-pdfs/683689.pdf

Let me know your feedback and whether the above suggestion was helpful.

Thank you.

Regards,

Kelly Jialin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Kelly,

Thanks for the information. I have followed your suggestion and followed every details. However, I got the same error messages.

Joseph

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Have you tried adding in and naming it as jtag_uart in platform designer? You may follow the user guide here: https://www.intel.com/programmable/technical-pdfs/683689.pdf Section 3.6.5.5.4. Add the JTAG UART

If the issue still persists, it is recommended you update the Quartus version used to avoid errors.

Thank you.

Regards,

Kelly

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Kelly,

I am designing the Nios II for a course assignment, one requirement of which is to use the "sdram controller IP". Only the Quartus Prime Lite 17.1 supports this IP. Unless there is a way to add this IP in the other more updated versions of Quartus Prime Lite, my assignment will be stucked.

Thank you for your attention and help.

Joseph

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Just to confirm whether did you insert System ID(sysid) and jtag_uart IPs in your platform designer for your design?

SDRAM controller IP supports up to 20.1 lite version, but however there will be IP upgrades for your design that may require extra effort on debugging.

Hope to hear on your feedback.

Thanks.

Regards,

Kelly

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Any updates from your end whether the information provided was useful to solve your issue?

Thank you.

Regards,

Kelly

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kelly,

Your comment gave some clues to solve the problem.

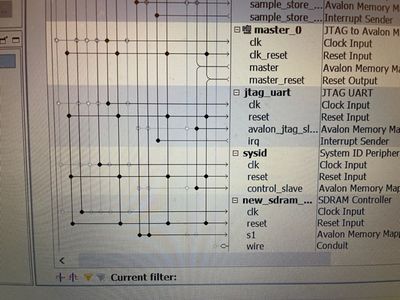

The photo attached shows System ID(sysid) and jtag_uart IPs were inserted and the names were changed to required names in Platform Designer. Why were there errors for these two IPs while the other IPs worked fine?

I am still working on it.

Joseph

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank yo for your response, but after you added in the sysid and jtag_uart IP and name them according to the user guide, do you still get any errors?

Hope to hear from you. Thank you.

Regards,

Kelly

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Any updates from your end from your end? Is the feedback provided useful?

Regards,

Kelly

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Any feedback from your end? Have you managed to eliminate the errors after adding the correct IP names?

Thank you.

Regards.

Kelly

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Kelly,

I have been trying all possible ways to eliminate the errors. There is still no luck.

Thank you for your attention.

Joseph

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Could you try using the Nios II SBT design template, and select the Hello World template. Then, you should regenerate a new BSP to see the mismatch of names come from the new BSP, or you were using the old BSP generated with the wrong name.

Also, what is the FPGA development kit you are using for your project?

Hope this helps.

Thank you.

Regards.

Kelly

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Kelly,

I am using DE-10 Lite board.

Good news: The "Hello World" template was used to generate BSP with sysid changed to sysid_qsys, everything worked perfectly without any errors. The elf file was generated and run paired with the hardware design, things went smoothly. The conclusion is that there is something wrong with the given files.

Thank you for your suggestions and support.

Joseph

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

Thank you.

Regards,

Kelly Jialin, GOH