- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm trying to create a simple large adder 1728bits + 1728bits and check its fmax from the device. However, Quartus Prime V21.3.0 gave me some inaccurate Dedicated Logic Registers count. May I know which part actually goes wrong? Or is there any specific setting I have to aware of?

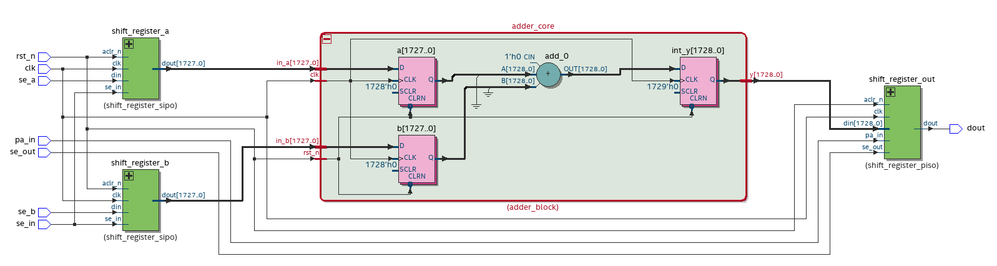

First diagram showing the RTL viewing of my design, it is just 3 main components, SIPO shift registers for input a and input b, then PISO shift register for output and the main adder body which include both input and output registers.

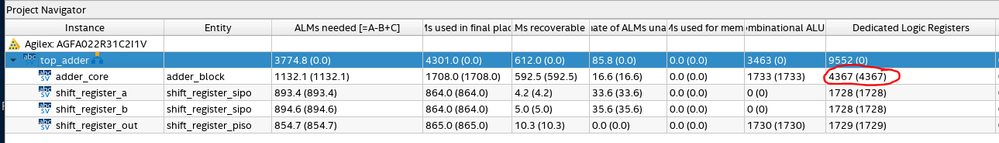

After the full compilation, the number of Dedicated Logic Registers given by Quartus is 4367x for adder_core instance, which is incorrect. Isn't it suppose to be 5185x (1728+1728+1729).

Full set of my verilog code is attached in this tread.

Any expert, please advise.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

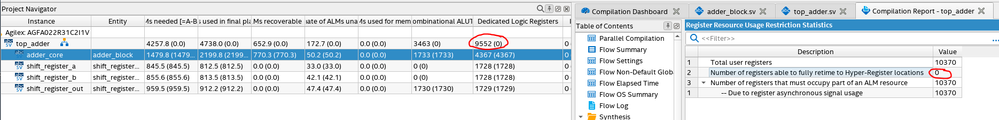

Since this is an Agilex device with Hyperflex, some of the registers may have been retimed into hyper-register locations. I think the register count may only show registers that have remained in ALMs, not registers that were retimed into hyper-registers. Check the Hyper-Retiming report in the compilation report to correlate if this is the case.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell,

thanks for your reply. I check on the hyperflux register usage. Sadly, the number isn't matched.

Under the "Register Resource Usage Restriction Statistics" panel, I see zero hyper register and total register of 10370 (correct number of my expected registers count). However, the "Dedicated Logic Registers" under Project Navigator showing 9552x registers. Some are missing.

Also, I tried on a smaller adder size 864 bits (a) + 864 bits (b) and other smaller adder combination, all the register count are accurate to my expectation. Just when the adder size is getting bigger to 1728 bits +1728 bits, then Quartus showing me this incorrect number of register count.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This case will be put to close pending. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page