- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi All

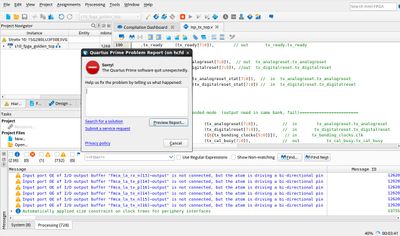

in Quartus22.4 , I use a fpll as transceiver pll , but it can not lock , but it can lock when I use Quartus21.1 , dose any one have this problem , or what should I do , I use Quartus22.4 because Quartus21.1 will crash when the transceiver is 8 channel

I tried many ways to lock fpll , even the reference clk direct from pin , it still unlock !!

Thanks

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi King22,

Thanks for the project file. I am able to reproduce the crash so I will make a report to engineering to fix it in future release.

As for the fpll can't unlock in Quartus 22.4, can you continue the communication in another forum that was posted by you?

I believe that was supported by another AE in that post.

I will close this one. Is it okay for you?

Regards,

Aqid

링크가 복사됨

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hello,

Thank you for reaching out Intel FPGA Community.

Can you share the design for me to reproduce it from my side?

I need to confirm first if this is a bug or not.

You can choose to share it directly or through email. Please let me know.

Regards,

Aqid

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Aqid

my OS is : CentOS Linux release 7.9.2009 (Core)

and I check fpll lock status by signal_tap stp1.stp

the signal name in stp is " isp_fpga_clk_locked "

Thanks

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

Can you share the design with .qar file format? I can't reproduce the design from the attached file that you provided.

Please let me know if you want me to initiate the email for you to share the .qar file.

Regards,

Aqid

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Aqid

Sorry I forgot to tell you , Quartus version that I use are quartuspro22.4 & quartuspro21.1(not quartus21.1)

BRs

King22

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Never mind, I managed to open the file.

I tried to compile the design in Quartus 21.1 and got the compilation error. Can you explained how it crash from your side? If this is a bug, I can report it to the engineering team.

For Quartus 22.4, so far, I compiled the design successfully. Will tried to look on the issue with the transceiver fpll can't lock. If you can explain the steps you do maybe it can help me to further investigate. It will be very appreciated.

Regards,

Aqid

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Aqid

1. I can't find any *.qar in my project

2. I can finish the attaced project with Q21.1 (tranceiver is 4 channel) , Q21.1 will crash on my side when I use the tranceiver over than 4 channel , I had report the situation already and got a reply , Intel suggess me to change the Quartus to 22.4 , so my company upgrade it .

3. About how to check the lock status of FPLL , I just use a signal tap file attached in my project , the file name is "stp1.stp" ,

the signal name in stp is " isp_fpga_clk_locked " . In Q21 , this signal will be "1" , and in Q22 result , this signal always "0"

Thanks

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hello,

- Can you share the project file with more than 4 channel for me to reproduce the Quartus crash on version 21.1?

- Thank you for the explanation. I will reproduce it from my side.

Regards,

Aqid

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Aqid

attached project is 8 lane transceiver , I use quartus prime pro 21.1 and got crashed ,

, the same project run in quartus prime pro 22.4 will finish smoothly , (but have fpll unlock issue)

BRs

King22

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi King22,

Thanks for the project file. I am able to reproduce the crash so I will make a report to engineering to fix it in future release.

As for the fpll can't unlock in Quartus 22.4, can you continue the communication in another forum that was posted by you?

I believe that was supported by another AE in that post.

I will close this one. Is it okay for you?

Regards,

Aqid