- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All

I use s10 fpga , and the compiler is quartus22.4 , in my design , I use a fpll as transceiver pll , but the fpll can not lock , but when I use quartus21.1 to compile , fpll get locked .

I use quartus 22.4 because quartus21.1 will crash when transceiver channels more then 4 channels ,

If any one can help me ,or any one can get fpll locked in quartus 22.4

thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you please provide your design files to reproduce the error at our end?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ash_R_Intel

Attached is my project

This question you can reference below link , I post it and FPLL still not locked in quartuspro 22.4

Solved: quartus22.4 fpll unlock - Intel Communities

note : Quartus version that I use are quartuspro22.4 & quartuspro21.1

Regards

King22

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I found the problem to be related to cascading of the IOPLL to the FPLL. For the S10 devices, this arrangement is not allowed. Please refer to the documentation links below:

https://www.intel.com/content/www/us/en/docs/programmable/683621/current/fpll.html

This is also clearly visible from the RTL Netlist Viewer against Technology Map Viewer. The RTL viewer is the logic that you intend, whereas the Technology Map viewer is the design that you get.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ash_R

So transceiver fpll (FPLL1) can use another cascade fpll (FPLL2) as reference source ,

if this is true , Can FPLL2 's reference clock source from IOPLL like below,

IOPLL-> FPLL2->FPLL1->Tranceiver

In my real design , IOPLL will change , so I wish when IOPLL change ,

the transceiver output data rate will auto changed also.

Regards

King22

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No, the IOPLL -> FPLL2 itself will not work, meaning they cannot be physically connected. So, even this arrangement is not feasible.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ash_R

I will try the reference clk direct from differential pair , but it will limited my design ,

by the way , The same project processed by Quartuspro 21.1 work well , fpll can get locked , and function is correct,

so I think there is a way form IOPLL to FPLL, may be different Quartus version process the design different way .

BRs

King22

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am currently checking the scenario that you explained for version 21.1 on board. Please give me some time to test and get back to you.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi King22,

I helped Ashlesha to see whether can get the fpll lock in our board for Q21.1.

However, we have problem to see the fpll can lock in the signal tap in Q21.1 as you said. Can you share the snapshot of the signal for "isp_fpga_clk_locked" in Q21.1?

Another thing is, we would like to try using simulator tools to see if we can see the waveform from the fpll locked. Do you have the testbench file (.tb) so that I can check the signal from the simulator?

Regards,

Aqid

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi AqidAyman

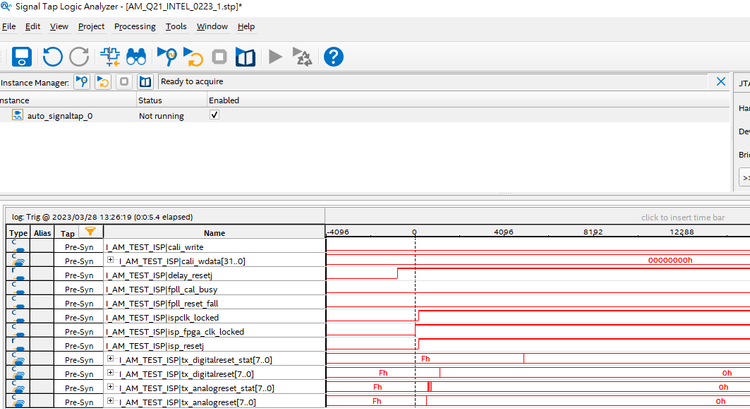

1. Attached fig is snapshot of the signal for "isp_fpga_clk_locked" in Q21.1 after I push the HW_RESET on the board ,

"isp_fpga_clk_locked" will go high in the fig

2. Sorry I do'nt have .tb file for simulation

BRs

King22

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello King22,

Appreciate the snapshot provided.

Do you have the time to help us creating the .tb file from your design to simulate that signal? If you can't, then it's okay. Just let me know.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi AqidAyman

I am sorry. I am busy now ,

so I don't have time to build the test bench.

BRs

King22

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi King22,

No problem.

The internal team ask for the confirmation on below situation that you faced:

- 21.1, 4 transceiver channels - crash with internal error

- 21.1, <4 transceiver channels - can compile, fpll can lock

- 22.4, 4 transceiver channels - can compile, fpll cannot lock

- 22.4, <4 transceiver channels - can compile, fpll cannot lock

Is it accurate?

Regards,

Aqid

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi AqidAyman

I modify first 2 item as below

- 21.1, >4 transceiver channels - crash with internal error

- 21.1, =<4 transceiver channels - can compile, fpll can lock

Above case is that , fpll's source is from io_pll

and if I use differential clk as fpll'a source , Q22.4's fpll will locked

BRs

King22

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi King22,

So, to make it simpler, this is what we got from your explanation as below. Can you help to see each one of the scenarios and confirm if it is accurate or not?

- 21.1, fpll's source = iopll, >4 transceiver channels - crash with internal error

- 21.1, fpll's source = iopll, =<4 transceiver channels - can compile, fpll can lock

- 22.4, fpll's source = differential clk, >4 transceiver channels - can compile, fpll can lock

- 22.4, fpll's source = iopll, >4 transceiver channels - can compile, fpll cannot lock

- 22.4, fpll's source = differential clk, =<4 transceiver channels - can compile, fpll can lock

- 22.4, fpll's source = iopll, =<4 transceiver channels - can compile, fpll cannot lock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi AqidAyman

Above 6 scenarios are true for my experience

BRs

King22

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi King22,

Thank you so much for your help to verify the scenarios you faced.

The engineering team is now investigating this issue, and it may take some time.

Really appreciate your understanding. I will update back to you once got any updates from them.

Regards,

Aqid

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It seems that this case have take quite some time now.

Is it okay if I contact you by email if I have the updates from the engineering team regarding this issue?

As for now it seems will take some more time for them to focus on this. I really apologies for this and I appreciate your understanding.

Regards,

Aqid

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous question/reply/answer that we have provided, please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi AqidAyman

You can contact me by email if I have the updates from the engineering team regarding this issue

Regards

King22

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page