- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I have a set of signals passing between asynchronous clock domains in an spi slave module.

I get the following warning when i try to add the max skew constraint

Warning (332182): No path is found satisfying assignment "set_max_skew -from [get_keepers {*spi*shift_reg*}] -to [get_keepers {*spi*rx_data_reg*}] -get_skew_value_from_clock_period min_clock_period -skew_value_multiplier 0.800 ". This assignment will be ignored.

The exact command from the sdc file is also included

set_max_skew -from [get_keepers {*spi*shift_reg*}] -to [get_keepers {*spi*rx_data_reg*}] -get_skew_value_from_clock_period min_clock_period -skew_value_multiplier 0.8

Thanks

Jay

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hey,

I have the exact same problem. https://community.intel.com/t5/Intel-Quartus-Prime-Software/Crossing-Clock-Domain-Problems-Timing-Analyser-ignores-set-max/td-p/1308590 .

However it works during the place and route and also the designs output is correct. I can not detect any metastability.

Am I right assuming that this error just occurs while using the Timing Analyser and no error is thrown during compilation?

Sadly I also got no answer as do other people with the same question (looking through the forum it gets asked at least once a week I would say).

Best regard

Christian

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jaya,

From the warning told, I can see the path is not there. Can you try to report timing the path for that and see if it is valid?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

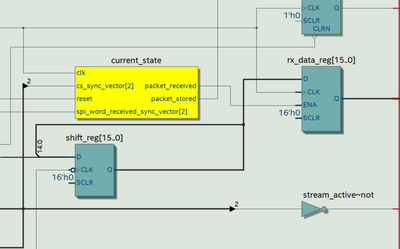

I have attached the screenshot from the RTL viewer. Both the registers are clocked by asynchronous clocks and I have declared the clocks as asynchronous by using clock groups.

Report max skew summary turns up empty.

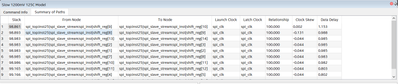

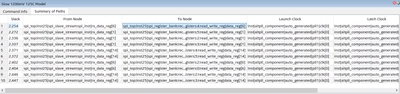

I can see the setup/hold details for the individual registers.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Jay,

Can you set the max skew again and this time using node finder in TA to verify the path?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Syafieq,

I couldn't find the Node finder in TA. I can see that option in RTL viewer. Is that what you meant?

I reran the SDC file by removing the asynchronous clock grouping and the skew command was executed and didnt generate a warning.

set_clock_groups -asynchronous -group [get_clocks {spi_clk spi_virt_clk}]

set_max_skew -from [get_registers {*spi*shift_reg[*]*}] -to [get_registers {*spi*rx_data_reg[*]*}] -get_skew_value_from_clock_period min_clock_period -skew_value_multiplier 0.8

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jaya,

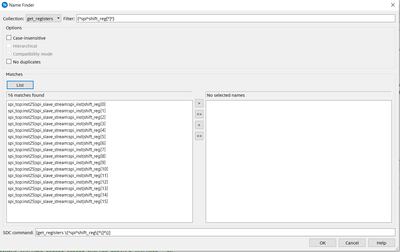

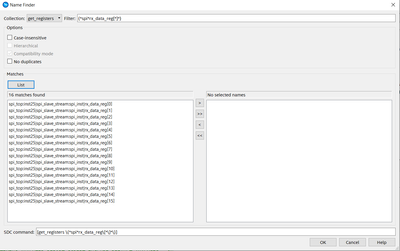

What I mean is you can use use the Name Finder to search the path and collection for path verification.

If they are CDC (need to double confirm again, roughly judging, both are not related clock obviously), and removing the set group and set skew result no warning, I afraid your design will hit metastability without proper constrain. Maybe you can take a look at below how related to CDC consideration.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Syafieq,

I was following the guidelines in the article you shared.

I created a clock group with only the spi clk and spi virtual clock

# Create clock group for SPI clk

set_clock_groups -asynchronous -group [get_clocks {spi_clk spi_virt_clk}]

Then i created the net delay and max skew constraints

# Set net delay between spiclk to sys clk data crossings

set_net_delay -from [get_registers {*spi*shift_reg[*]*}] -to [get_registers {*spi*rx_data_reg[*]*}] -max -get_value_from_clock_period dst_clock_period -value_multiplier 0.8

# Set max skew between spiclk to sys clk data crossings

set_max_skew -from [get_registers {*spi*shift_reg[*]*}] -to [get_registers {*spi*rx_data_reg[*]*}] -get_skew_value_from_clock_period min_clock_period -skew_value_multiplier 0.8

Only the max skew command generated warning. The net delay command using the same search keywords found the path.

Warning (332182): No path is found satisfying assignment "set_max_skew -from [get_registers {*spi*shift_reg[*]*}] -to [get_registers {*spi*rx_data_reg[*]*}] -get_skew_value_from_clock_period min_clock_period -skew_value_multiplier 0.800 ". This assignment will be ignored.

Info (286030): Timing-Driven Synthesis is running

Warning (332182): No path is found satisfying assignment "set_max_skew -from [get_registers {*spi*shift_reg[*]*}] -to [get_registers {*spi*rx_data_reg[*]*}] -get_skew_value_from_clock_period min_clock_period -skew_value_multiplier 0.800 ". This assignment will be ignored.

Warning (332182): No path is found satisfying assignment "set_max_skew -from [get_registers {*spi*shift_reg[*]*}] -to [get_registers {*spi*rx_data_reg[*]*}] -get_skew_value_from_clock_period min_clock_period -skew_value_multiplier 0.800 ". This assignment will be ignored.

I tried by commenting out only the clock group command. Then the max skew and net delay commands gave no warnings.

The net delay command works and doesnt generate a warning.

If i comment out the set_clock_group command then the max_skew command executes and doesn't generate a warning.

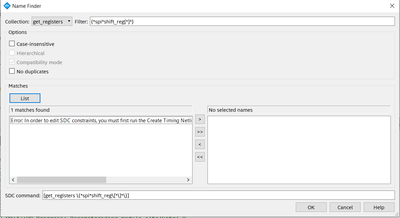

I also tried to use the name finder as you suggested to see the response. I get an error showing that, first create timing netlist must be run. I think in the normal compilation flow, the sdc are executed after the netlist is created. so this command should work as it does for other commands.

In the TA, I am able to see the registers using the get registers command:

Regards

Jay

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Syafieq, I hope you got a chance to review my above post. I can see the effect of the constraints in the chip planner when the warnings go away if i remove the clock grouping but keep the net delay and max skew constraints.

Regards

Jay

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jaya,

Can you change your constrain as below as see if reflect any changes?

From:

set_clock_groups -asynchronous -group [get_clocks {spi_clk spi_virt_clk}]

To:

set_clock_groups -asynchronous -group [get_clocks {spi_clk}] -group [get_clocks {spi_virt_clk}]

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Syafieq,

I can attempt that. Could you explain why I should put the clk and related virtual clock in two groups? I do expect those clocks to be related and the paths between them to be analyzed. The spi_clk and spi_virt_clk are used to analyze the spi interface and the virtual clock is to constrain the IO of the SPI interface.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hey,

I have the exact same problem. https://community.intel.com/t5/Intel-Quartus-Prime-Software/Crossing-Clock-Domain-Problems-Timing-Analyser-ignores-set-max/td-p/1308590 .

However it works during the place and route and also the designs output is correct. I can not detect any metastability.

Am I right assuming that this error just occurs while using the Timing Analyser and no error is thrown during compilation?

Sadly I also got no answer as do other people with the same question (looking through the forum it gets asked at least once a week I would say).

Best regard

Christian

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Christian for the update. I haven't encountered any timing issues (yet) but I do get the warnings in the compilation.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jaya,

You might need to see below KDB which affect 20.4 and prior Quartus user. This may affect the source destination when trying to set the skew of your constraint. Can you try instead of specify get_value_from_clock_period dst_clock_period -value_multiplier 0.8, you put the value straight away but this time applied to set_max_skew constraint and see if it applicable. The reason is set net delay are able to work for above KDB when specify the value directly.

https://www.intel.com/content/www/us/en/support/programmable/articles/000085880.html

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I had a similar issue: it happens in Standard Edition 18.1 -- 20.1, but does not happen in Quartus Pro 22.2

set_clock_groups -asynchronous *does* impact set_max_skew on Standard 18.1-20.1 but not on Pro 22.2