- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Whereabouts can I find some example timing diagrams for data transmission from PC into vJTAG on an FPGA?

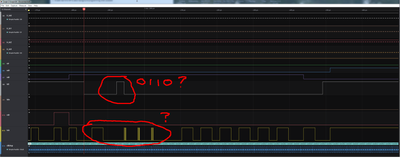

I am trying to make sense of what this command does with my logic analyzer but I cannot see the data in the diagram. Even if I *think* can see the data, the TCK signal doesn't seem to correspond to the bits on the TDI signal.

device_virtual_dr_shift -instance_index 0 -length 32 -dr_value 6

So I expect to see a 32 bit transmission that looks like this:

01100000 00000000 00000000 00000000

or

00000000 0000000000000000 00000110

Is the white blip in the below trace the 0110 bits? Why does tck not show 2 cycles within that period if this is the case?

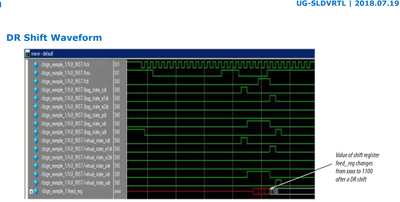

Surely there are some example timing diagrams I can refer to for example data transmission? I can't find any in the Virtual JTAG Intel FPGA IP Core User Guide - at least I cannot find a good example which is clear. I found the DR Shift Waveform but this shows a tidy TCK signal in Modelsim.

Is my logic analyzer not showing TCK correctly??

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for contacting Intel community.

We do not have other references other than the userguide for this IP. Have you follow the userguide or is there any changes made?

What is the quartus version that was used ? What is the FPGA that was used?

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using Quartus Prime 20.1.0 Lite Edition with a Cyclone IV FPGA (EP4CE6E22C8).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry, but I do not see the relationship between those two images. What is the exact problem that you encounter?

If you have follow the userguide, you will get the same output as shown in the userguide. Have you follow the steps in userguide one by one?

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We do not receive any response from you to the previous answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I requested a diagram that shows the TCK signal because what I see on my Logic analyzer makes no sense to me. Thankfully I sorted out my problem, but it would be nice to see a real diagram that shows how everything does relate to TCK in the real world - rather than an ideal simulator screenshot.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page