- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I’m working on arria10 and have developed my own board to phase with arria 10. I need to enable 2 spi, after following the doc Building Bootloader for Cyclone V and Arria 10 1 with my own hps.xml, quartus version 22.4pro, uboot version 21.04, the board is booted up with only one spi enabled. With some debugging, I find that the default device tree file (socfpga_arria10_socdk.dtsi) only enables 1 spi. So how should I generate the new device tree file, please? based on the doc, from 20.3pro, bsp editor is not used any more.

Tried change the socfpga_arria10_socdk.dtsi below to enable spi0(spi1 is default from socfpga uboot), but uboot stucked at reset peripherals

"Deasserting all peripheral resets\n"

then reboot again, never goes to linux.

--------------------------------------------

&spi0 {

status = “okay”;

};

&spi1 {

status = “okay”;

resource-manager@0 {

compatible = "altr,a10sr";

reg = <0>;

spi-max-frequency = <100000>;

/* low-level active IRQ at GPIO1_5 */

interrupt-parent = <&portb>;

interrupts = <5 IRQ_TYPE_LEVEL_LOW>;

interrupt-controller;

#interrupt-cells = <2>;

a10sr_gpio: gpio-controller {

compatible = "altr,a10sr-gpio";

gpio-controller;

#gpio-cells = <2>;

};

a10sr_rst: reset-controller {

compatible = "altr,a10sr-reset";

#reset-cells = <1>;

};

};

};

any hints?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

So you are using a custom board correct?

What are the full list of item changes (DDR, part number, etc) you made from the Arria 10 SoC Dev Kit?

Could you share your full boot logs?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Any update from your side?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please check your Quartus HPS IP settings and the device tree again.

You may need check the differences vs the Dev Kit, and change accordingly to your custom device from the default settings as the GHRD is based of the A10 SoC Dev Kit.

As we do not receive any response from you on the previous question/reply/answer that we have provided. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks for the help!

I have solved the uboot issue problem by using linux kernel generated dtb files instead of uboot generated one.

and the dtsi file modified below to enable 2 spidev, and seems it works,

&spi0 {

status = "okay";

spidev@0{

compatible = "spidev";

reg = <0>;

spi-max-frequency = <4000000>;

};

};

&spi1 {

status = "okay";

spidev@0{

compatible = "spidev";

reg = <0>;

spi-max-frequency = <4000000>;

};

};

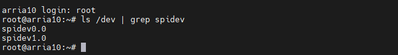

I have check the board /dev with below while didn't have a chance to test.

any comments are welcome, sorry for late feedback.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page