- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

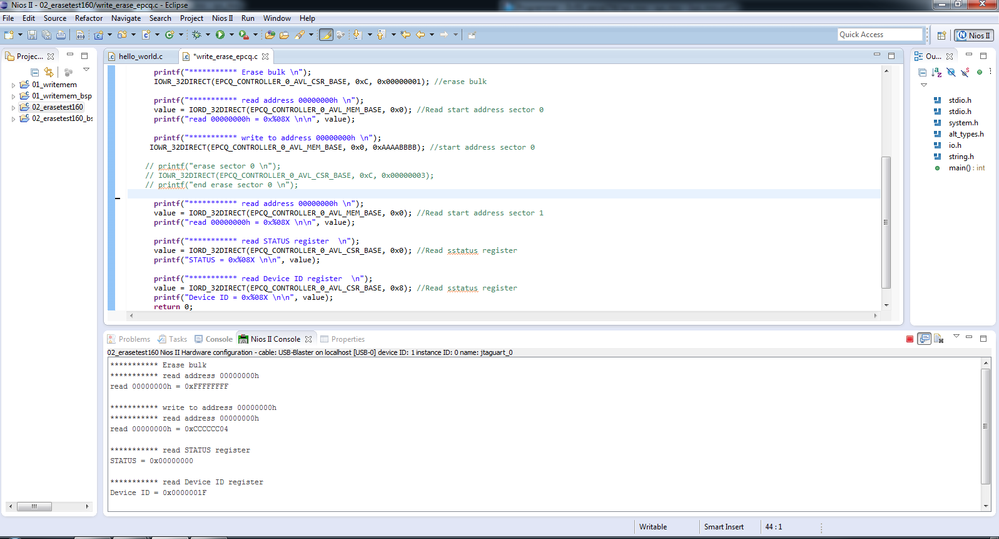

I am trying to access in read and write my EPCQL-1024 from simple soft running in NIOSII. I have the Altera Serial Flash Controller I configured in QUAD mode connected from its avl_csr and avl_mem to the NIOSII. I have tried to access in read and write the EPCQL registers (STATUS, Device ID) and the controller registers FLASH_ISR, or FLASH_IMR, it have been successful. But when I need to erase sector or write to memory. Here lies my problem; I can run nothing on board until power off. When reading the values back from the EPCQL or execute a simple access , it seem to return erroned values. I also tried reading the status register to see if there are processes occurring, but it always reads 0x0. Also when I try to read either the FLASH_ISR, or FLASH_IMR, the EPCQL seems to stop responding and I need to repower the chip then reload my .sof , the read data are correct. I am not sure where to start debugging this and if t's by definition, a flash memory needs a power off after each write operation, then how to write many data at a time to same or different sectors. Any help or points in a direction would be much appreciated.

Thank you in advance :)

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page