- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

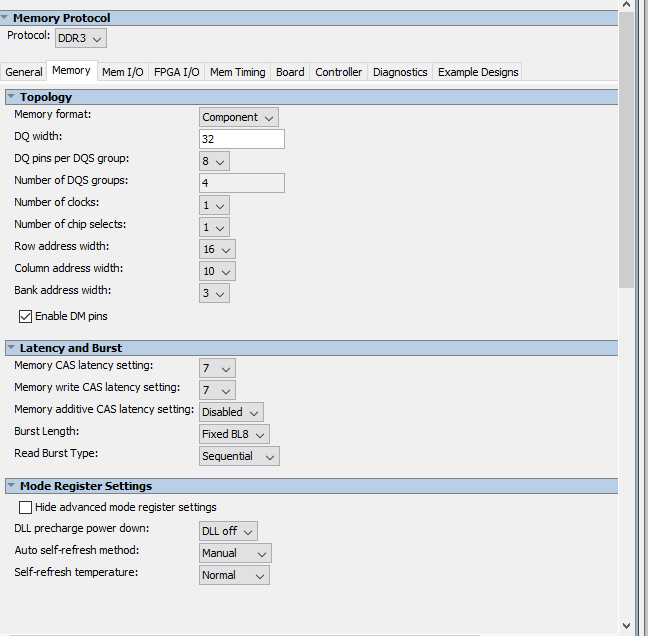

The above is the ddr config we kept

Previously our CAS latency for read for our DDR3(MT41J128M16JT-125) in our board connected to ARRIA10 SOC (10as016e4f27e3sg) is 11 and we tried to change it to 7 and then that bin file onwards our soc stopped booting and the log is attached.

The thing we want to confirm is will there be any effect of this on the ddr read and which affects the arm boot.

1 Solution

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir, Incorrect CAS latency setting might cause the DDR calibration fail. However, from the log file, I don't see any failure include the booting also seem successful.

Link Copied

1 Reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir, Incorrect CAS latency setting might cause the DDR calibration fail. However, from the log file, I don't see any failure include the booting also seem successful.

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page