- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello:

I will be very grateful if someone solve my problem. I was puzzled with it for a long time but I can't fine a proper way to solve it.

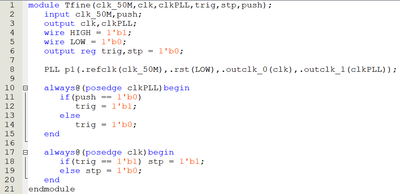

Program:

-----------------------------------------------------------------------------------------------------------

module Tfine(clk_50M,clk,clkPLL,trig,stp,push);

input clk_50M,push;

output clk,clkPLL;

wire HIGH = 1'b1;

wire LOW = 1'b0;

output reg trig,stp = 1'b0;

PLL p1(.refclk(clk_50M),.rst(LOW),.outclk_0(clk),.outclk_1(clkPLL));

always@(posedge clkPLL)begin

if(push == 1'b0)

trig = 1'b1;

else

trig = 1'b0;

end

always@(posedge clk)begin

if(trig == 1'b1) stp = 1'b1;

else stp = 1'b0;

end

endmodule

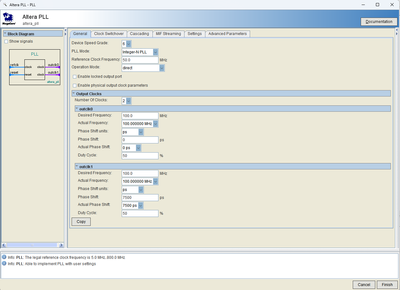

PLL setting:

-----------------------------------------------------------------------------------------------------------

When I'm tring to simulate on University Program VWF, I got two errors:

-----------------------------------------------------------------------------------------------------------

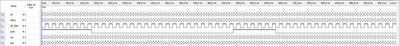

Waveform:

-----------------------------------------------------------------------------------------------------------

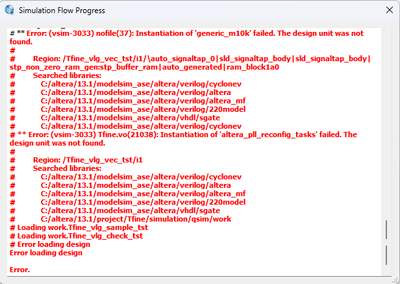

Error:

# ** Error: (vsim-3033) nofile(37): Instantiation of 'generic_m10k' failed. The design unit was not found.

# ** Error: (vsim-3033) Tfine.vo(21038): Instantiation of 'altera_pll_reconfig_tasks' failed. The design unit was not found.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This error is encountered when subcomponents are not found during compilation or elaboration. You are mostly instantiating a PLL IP top level module and the inside modules are not visible to you. For the IP to compile you need to include the device libraries as well. The best way is to generate the simulation script while generating the IP and refer it to get info on all the files and libraries are required to simulate the IP.

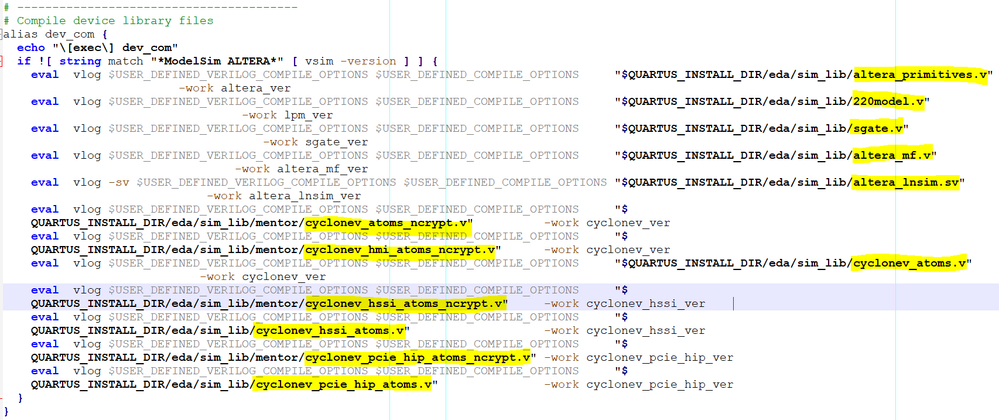

For example, to simulate a Cyclone V PLL IP in Modelsim, the script (msim_setup.tcl) compiles and use device related files as shown in the figure below:

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This error is encountered when subcomponents are not found during compilation or elaboration. You are mostly instantiating a PLL IP top level module and the inside modules are not visible to you. For the IP to compile you need to include the device libraries as well. The best way is to generate the simulation script while generating the IP and refer it to get info on all the files and libraries are required to simulate the IP.

For example, to simulate a Cyclone V PLL IP in Modelsim, the script (msim_setup.tcl) compiles and use device related files as shown in the figure below:

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page