- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

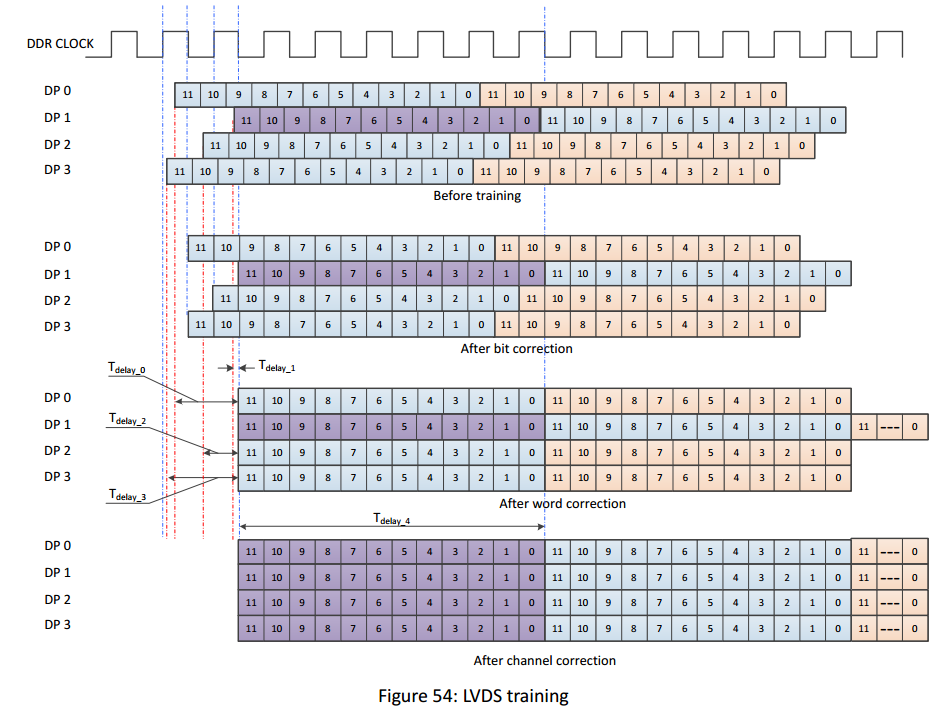

I’m going to Receive LVDS signals(data rates : 600Mbps) with FPGA (Cyclone V), There are 8 LVDS signals,12bit per channel from an image sensor, The sensor manual states that there is a difference in phase between these LVDS signals and that the signal should be trained before acceptance.

As shown, the training is divided into bit correction、word correction and channel correction. The sensor development board uses the xilinx FPGA, which uses iodelay, bitslip and shift_register to complete 3 corrections.

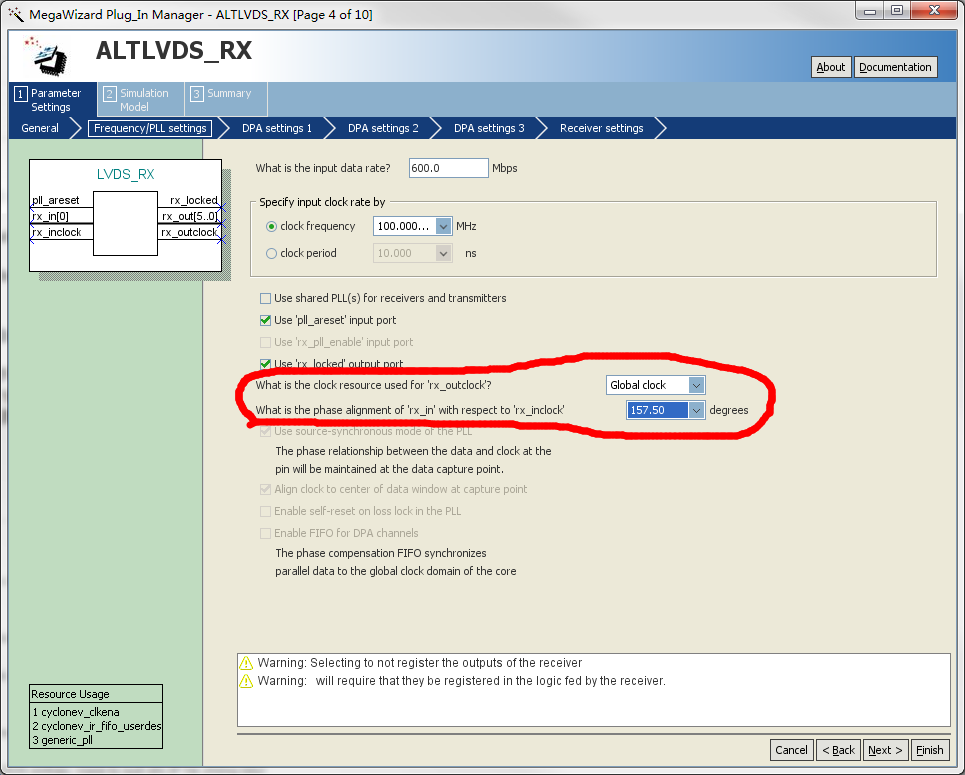

Now I’m using Intel FPGA Cyclone V 5CEFA5U19I7N where is no iodelay function, I don't know how to complete the bit alignment. I tried to use the ALTLVDS_RX core to receive 8 LVDS signals directly. As shown in the figure below, the phase difference between 'rx_in' and 'rx_inclock' can be set in the IP core. I can change this value to receive some stable LVDS data, but it cannot get 8 stable LVDS data At the same time, I know this is because there is a phase difference between the LVDS signal which is not synchronous with the DDR_clock and I did not do bit correction.

So I want to know how to use Intel's FPGA to complete the bit correction, which can align the LVDS signal with DDR_CLOCK. I hope someone with similar experience or knowledge can help me.Thank you!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

BitSlip is incorporated into the ALTLVDS_RX IP. If you move to the last Receiver Settings tab, you will find the bitslip setting there. Here you can select how many pulses the bitslip should be and other settings.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank Abe for answering,I konw the BitSlip,it's for word correction, right? just like when the trainning word is 111111000000, and the word received is 1111100000001, then I can use the bitslip function to get 111111000000, My problem now is that my sampling clock and data are not aligned. I even can not receive the 111110000001. so I want to do the bit correction, thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi WMing,

I am also working with the same sensor and have the same problem as you. The problem is in Cyclone V you dont have a DPA right! (for the bit alignment!) Is it posible to use the ALTIOBUF and using the io_config iterface manually config the delays or maybe just using the input assignments(add_input_delay)? I wonder how you solved your problem.

On Xilinx you have the IODELAY2 and using the input CAL you will do the alignment automatically, having maybe a problem with overflows on the delay counter!!

so! hope to hear from you!!!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi WMing,

First of all, you could implement programmable IO delay (like Xilinx iodelay analog which you mentioned) on Cyclone V, both static from IO assignment and even dynamic, which I think you doesnt' need.

You must also write correct timing constraints for your I/O Source-Synchronous system (which your Image Sensor outputs) for PLL to properly adjust clock phase.

Best regards,

Ivan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page