- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

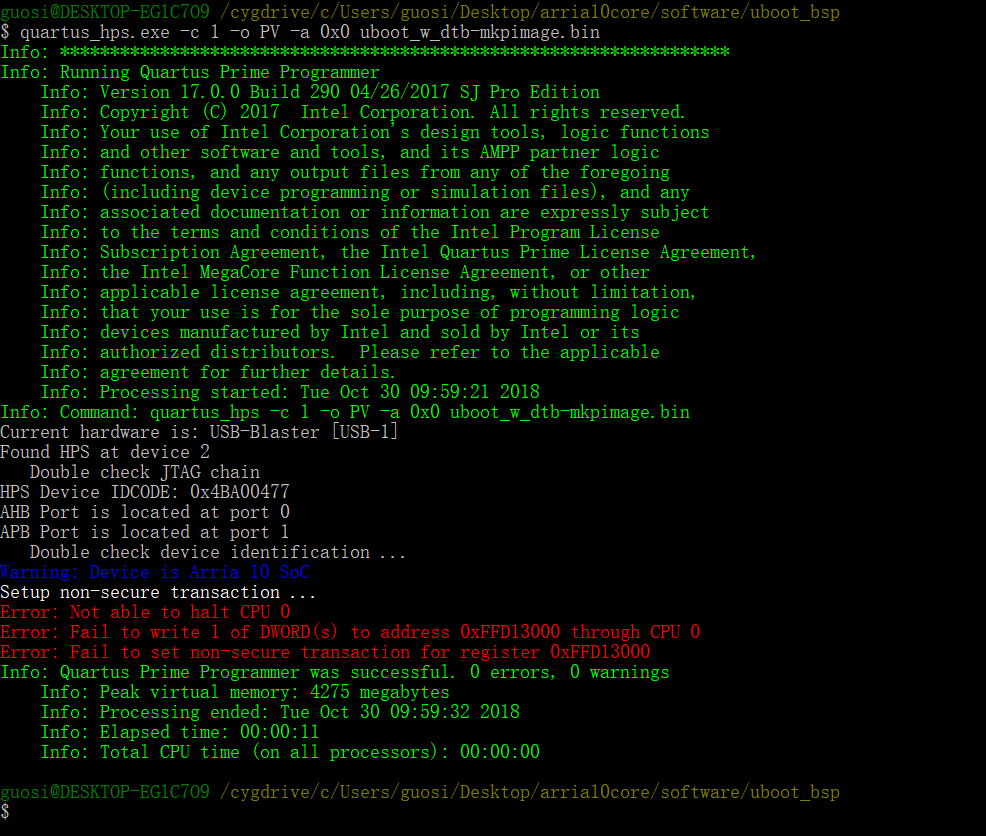

I tried a lot of ways to download uboot to QSPI FLASH through the directive of quartus_hps. However, there will be errors.

Error:Not able to halt CPU 0

Error:Fail to write 1 of DWORD(s) to address 0xFFD13000 through CPU 0

Error:Fail to set non-secure transcation for register 0xFFD13000

What should I do?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Refer the link below which may help in debug

https://www.youtube.com/watch?v=5qxyEaO8C5o

https://rocketboards.org/foswiki/Documentation/GSRD131QspiProgram

Best Regards,

Anand Raj Shankar

(This message was posted on behalf of Intel Corporation)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your reply,I have learned the tutorial refer to https://rocketboards.org/foswiki/Documentation/A10Gsrd170QspiBoot

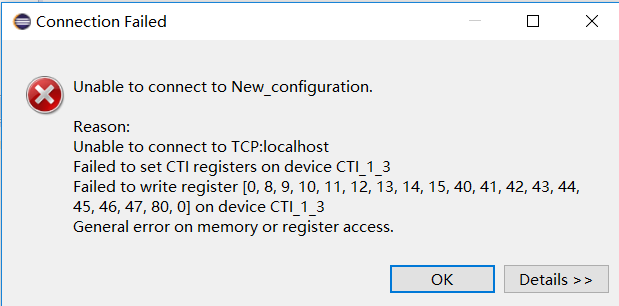

but I did not solve this problem.I designed a board using ARRIA10 SOC.When I download uboot to QSPI FLASH,The error information is shown in the figure1.Then I debug bootloader using ARM DS-5.The error information is shown in the figure2. What should I do?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

have u selected the correct msel settings to boot from qspi?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Were you able to make any progress on this? I'm getting the very same responses, trying to load U-Boot to a QSPI device with quartus_hps. The FPGA has configured properly from it's own QSPI device. The HPS has its QSPI device where U-Boot should load from. I have confirmed BSEL is pulled up and down to BSEL[2:0] = 0x6 (1.8V QSPI).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

First, confirm that you have pullup resistors (1KOhm) to 1.8VDC (VDD_IO) on HPS_nPOR and HPS_nRST pins.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page