- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello!

I am having difficulty using the IOWR and IORD functions in NIOS II.

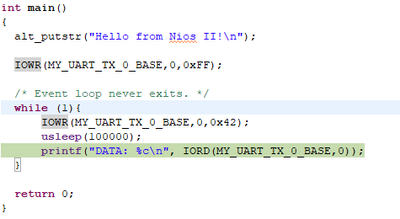

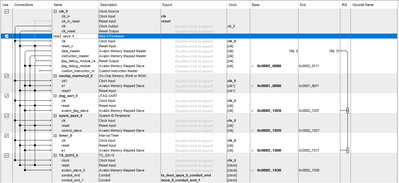

I have created a custom Uart Tx IP and I want to communicate with my computer through it. then, I have included it in NIOS II and then used Eclipse to store the desired characters in the Uart Tx IP base memory using the IOWR function.

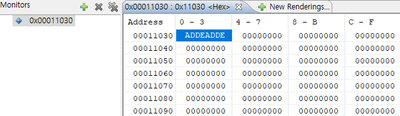

However, I found that the memory address where I stored the value is not working properly and is showing strange values instead of the values I stored. I thought it was a garbage value and initialized it, but the problem still persists. When I changed the offset from 0 to 1, the value was stored correctly at that address. I want to store the desired value at the desired memory address using the IOWR function. Am I doing something wrong? Or do you need more information to solve this problem?

Please let me know if you need more information. Thank you.

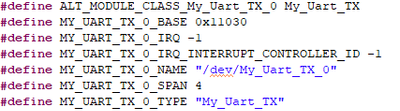

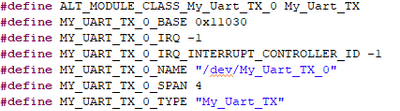

Debug (0x00011030 is my custom ip base address)

MY C code

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you share your .qsys for this? Also, which NIOS and Quartus version that you tested and build it on?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your answering

I'm now using Quartus 13.0sp1

beacuse this version is lastest version for cyclone ii

Here is my .qsys file link

https://drive.google.com/file/d/1rXqLX3zLWwuXYfy9pXj1LXsEr_Ty_Mjt/view?usp=share_link

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I see, I may need some time to get some info regarding the old 13.1 ver on if there are any known issues on the NIOS II with Cyclone II. Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This may take some time, I am still working on the issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you also provide the C code and your project file? I am trying to understand your C code flow.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is my C code.

//////////////////

//////////////////

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks, let me get back to you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Here is the description on the macros:

https://www.ecb.torontomu.ca/~courses/coe718/Data-Sheets/Nios-Lab/n2sw_nii5v2.pdf#page=113

IOWR(BASE, REGNUM, DATA), where REGNUM should be the offset address of BASE.

Are you facing any other issue?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you have any update?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you.

I received your answer well.

Even after modifying the code according to your answer and debugging it, the same problem occurs.

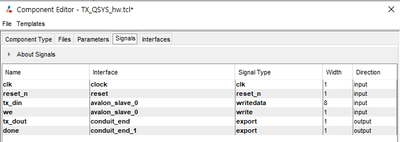

I think the problem is that I made my CUSTOM IP incorrectly.

If it’s not too much trouble, could you tell me how to make a CUSTOM IP using the UART_TX HDL code I’m providing?

I will write my HDL code for this purpose. I will also attach other HDL codes I wrote to make it into CUSTOM IP below.

// UART_TX

/*

// HDL CODE FOR USING CUSTOM IP

////////////////////////////////////////////////////////////

Thank you again for your dedication.

Thanks to this community, I was able to grow quickly

/////

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your feedback, for Custom IP creation, I am not familiar with it, could you create a new thread on Custom IP creation based on your request? A new expertise will assist you on that.

If there are no further related questions, we could close this thread and you can follow up in the new thread regarding the Custom IP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page